卷积码及其译码算法的仿真实现

[关键词:卷积码,译码算法,仿真] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,论文,仿真程序,答辩稿】 作品编号:txgc0905,word全文:33页,合计:12000字 |

课题研究内容:

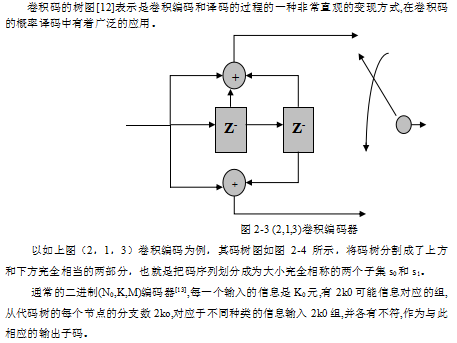

本次毕业设计内容包括:首先简单的介绍信道编码,译码的的基本概念,分类和原理,简单地讲述信道编码的发展过程。然后引入两类主要的信道编译码,即卷积码(在这里我们主要讨论卷积码)。其次介绍卷积码的概念,卷积码的原理和卷积码的描述方法。然后介绍卷积码的编译码算法,其中回顾维特比译码算法的研究背景及目前的发展状态的基础上重点介绍维特比算法的基本原理。最后对整个内容做个总结。

本次毕业设计内容包括简介卷积编码及译码算法,回顾维特比译码算法的研究背景及目前的发展状态,对卷积码的概念、基本原理及实现进行详细描述,在其基础上介绍维特比译码的基本原理。

这篇论文的研究的重点是使用Viterbi译码的卷积码编码器的点阵图算法计算路径度量,选择开始时间结束时间只幸存路径的最大似然路径沿着最大似然路径回到开始的时间,通过相应的路径编码输出是最大似然译码输出序列。它是一种最大似然译码方法,编码的约束长度,或不在错误率不是很高时,维特比译码设备相对简单,运算速度快,使维特比译码器被应用到了日常的各个领域。

本论文主要内容包括:

第一章 绪论 通过查询资料、文献,主要介绍了选题背景、课题介绍、卷积码的发展现状。

第二章卷积码概述 学习、介绍了卷积码的概念、基本原理以及它的各类表示方法。

第三章维特比译码的概念 介绍了维特比译码算法概念、基本原理。

第四章仿真过程的实现 在之前理论基础上对卷积码及其译码算法进行了仿真。

第五章结束语 主要是对所做的工作来一个总结以及有所展望。

结论

卷积码是一种纠错编码,纠错编码己有五十几年历史,早在1948年,香农(Shannon)在他的开创性论文“通信的数学理论”中,首次阐明了在有扰信道中实现可靠通信的方法,提出了著名的有扰信道编码定理,奠定了纠错码的基石。以后,纠错码受到了越来越多的通信和数学工作者,特别是数学家的重视,使纠错码无论在理论上还是在实际中都得到了飞速发展。 本文首先从数字通信的一些基本概念和差错控制编码理论出发,引入卷积码的一些基本理论,接着讨论了卷积码的编译码基本原理,对卷积码的表示方法和编译码算法做了简单的介绍,再通过编写卷积码的编码和解码程序,并且用MATLAB仿真软件进行仿真和纠错验证,并通过对不同码率、不同约束长度、不同回溯长度,以及不同判决方式情况下误码率的分析,得出以下结论:

(1)当编码约束长度不大,当码率一定时,随着信道噪声的逐渐减小,系统的误比特率也逐渐减小。

(2)当改变系统码率时,随着卷积码码率的逐渐提高,系统的误比特率也呈现出增大的趋势,也就是说码率越低,系统的误比特率就越小,误码性能就越好。对于二进制对称信道,当采用BPSK调制方式时,通常选取的码率为1/2。

(3)对于码率一定的卷积码,当约束长度N发生变化时,系统的误码性能也会随之发生变化,随着约束长度的逐渐增加,系统的误比特率明显降低,所以说当码率一定时,增加约束长度可以降低系统的误比特率,但是,随着约束长度的增加,译码设备的复杂性也会随之增加。所以对于码率为1/2的卷积码,在选取约束长度时一般为3~9。

(4)对于码率一定的卷积码,当反馈深度发生变化时,系统的误码率也会发生一定的变化,随着反馈深度的增加,系统的误码率呈下降趋势,但是通常在反馈深度大于或者等于约束长度的五倍时,误码率几乎不再发生变化,故常常取回溯长度为5N。

(5)对于码率一定的卷积码,采用的译码判决方式不同,也会对系统的误码率产生影响,一般来说,软判决译码性能要优于硬判决译码性能,但这是以提高设备复杂性为代价的。

| 提示:此毕业设计论文完整版包含【开题报告,论文,仿真程序,答辩稿】 作品编号:txgc0905,word全文:33页,合计:12000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——卷积码及其译码算法的仿真实现(开题报告,论文,仿真程序,答辩稿)!

当前位置:

当前位置: