QPSK调制器的CPLD实现之程序设计

[关键词:QPSK,调制器,CPLD] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0082,word全文:30页,合计:6000字 |

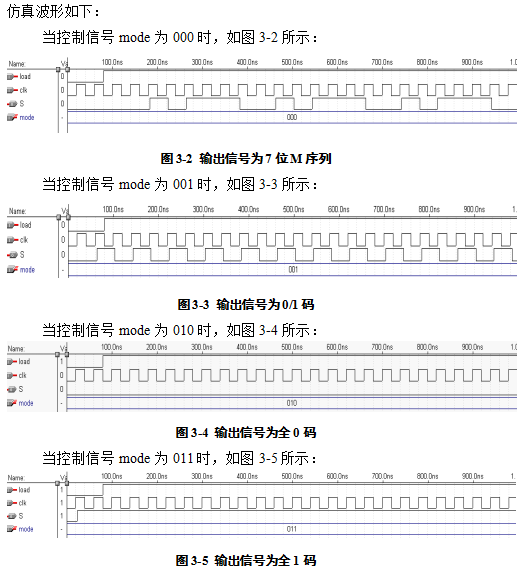

本论文介绍了数字通信中的QPSK调制原理,利用CPLD芯片进行QPSK调制器设计。将在MAX+plusⅡ环境下用VHDL语言编写程序,并进行模拟仿真得出波形图并和用示波器对电路板调试所得到的波形进行比较,验证本设计的正确性。本设计所研究的内容对通信原理实验的扩展非常有意义,具有较高的实用价值。

我的主要工作为:

1.查阅相关文献,了解QPSK调制解调的原理;

2. 熟悉在MAX+plusⅡ环境下用VHDL语言编程;

3.在MAX+plus II编译环境下,用VHDL语言编写QPSK调制器的程序,编译调试通过得出仿真波形;

4. 选择ALTERA EPM7064SLC-10和EPM7032SLC-10芯片,进行管脚配置,并且将相关的程序下载到CPLD元器件上;

5. 将仿真波形与同组另一同学做出的实际波形进行比较

通过多方面搜集资料,以及灵活运用以前所学的知识,熟练掌握了QPSK调制与解调的基本原理,VHDL语言的编程规则与运用,MAX+plusⅡ软件的应用,并在此基础上实现了基于CPLD的QPSK调制电路的设计。这次设计,我都是在不断地“构思—实现—改进—再构思—再实现”中一步一步循序渐进地完成本次设计的。在本次设计中,遇到了以下问题:

(1)在编写分频程序的过程中,寄存器的位数不够不能一次完成对4MHZ时钟4K分频。

(2)在模拟仿真过程中,由于仿真的时间太短造成波形不能完整的显示

(3)在发点过程中,出现不该出现的点。

(4)在D/A0832转换器中,对WR1引脚输入时钟的选择。

(5)在分配引脚的时候没有考虑到有些引脚不能做输入/输出口,在对CPLD芯片进行烧写时出现错误。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0082,word全文:30页,合计:6000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——QPSK调制器的CPLD实现之程序设计(论文)!

当前位置:

当前位置: