基于CPLD的小型加速度测试系统的设计

[关键词:CPLD,加速度测试系统] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0209,word全文:38页,合计:17000字 |

本课题主要研究在不同环境下的小型加速度测试技术。熟悉VHDL语言和CPLD的应用及ISE软件的操作,掌握测试仪的工作原理,根据要求设计出基于CPLD的小型加速度测试系统,编写控制程序,最后对程序进行调试,撰写毕业设计说明书。

结论

随着数据采集对速度性能的要求越来越高,CPLD有单片机无法比拟的优势。CPLD时钟频率高,内部延时小,速度快、效率高。虽然我国现代工业发展时间短,但适应于工业需求的数据采集电路的设计研究有了长足发展。

软件部分的设计

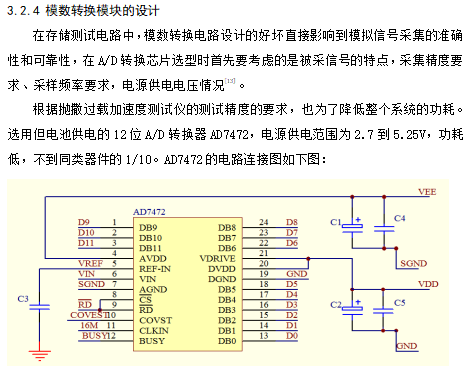

本系统采用CPLD作为中心控制器,设计需要的逻辑,内部逻辑相对简单,状态 。在动态参数的存储测试领域,测试仪要随被测体一起运动,要求测试仪具有体积小、功耗低以及抗过载等特点。抛撒过载加速度测试仪也具有动态测试的特点。根据系统所给指标,测试仪容量设计为512K*12bit,负延迟为128K*12bit,采样频率为100KHZ。

以VHDL语言设计中心控制器件CPLD的控制逻辑。逻辑流程图如图所示。测试仪上电初始化以后即开始循环采样,当系统感受到超过预设值的加速度信号,给出触发信号“TRI

之后,开始记录触发后的转换次数,计满一定值后,系统进入节能状态,等待计算机发读数指令将数据读出。

本文以CPLD为核心,对小型加速度测试仪电路进行了设计和研究,具体工作总结如下:

1)查阅相关资料,分析了小型加速度测试仪电路的研究和发展状况;

2)完成了基于CPLD的小型加速度测试仪电路,并对设计结果进行了模拟和仿真

3)根据需要进行了小型加速度测试仪电路相关实验,并分析了实验结果,为进一步的设计和电路性能的提高提供了可行的实验数据。

本课题经过了细致的方案设计,分层次分模块的硬件设计,最终达到了设计之初所要达到的指标,基本上完成了所要设计的内容。由于在实际设计的过程中遇到了很多以前没有接触到的问题,通过和导师、研究生师姐以及同学们的相互讨论、学习,不断的改进和完善设计最终达到了预期的设计目标。同时通过这次的设计,理论和实践得到了很好的结合,学到了很多知识,对于开发应用系统的流程有了一个完整的认识,对以后进一步学习也有很到的启发作用。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0209,word全文:38页,合计:17000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于CPLD的小型加速度测试系统的设计(开题报告,任务书,论文)!

当前位置:

当前位置: