基于CPLD的数据判断及传输模块的设计

[关键词:CPLD,数据判断,传输模块] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0166,word全文:36页,合计:8200字 |

本课题设计要解决的问题

本课题要解决的问题主要是对在数据传输的过程中出现的错误进行判断以使接收到想要的数据剔除掉那些不需要的数据,以实现串转并的数据传输。

本课题设计拟采用的研究手段

通过基本技术的学习和设计分析,判断有用的数据,以使接收到想要的数据剔除掉不需要的数据,借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆将代码传送到目标芯片中,实现设计的数字系统即使用VHDL语言进行计数器,串转并,移位寄存器的编写已实现我们的设计目的。

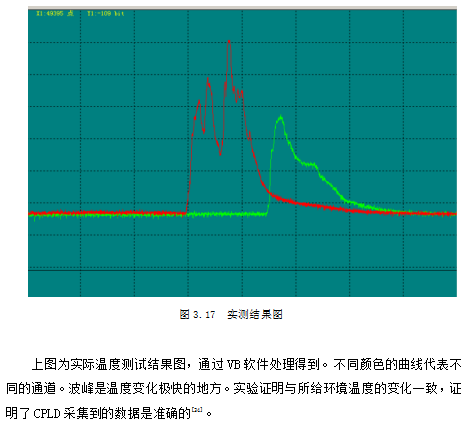

总体功能描述:本设计采用CPLD(XCR3128)作为主控芯片,是基于CPLD(XCR3128)内部宏单元数量多,并且有丰富的I/O口,传输速率比其他器件(比如单片机)要快,使设计更加灵活,该数据传输模块,由CPLD来判断和接收发数装置发送的带有头文件标志的数据,数据进入CPLD以后由内部移位寄存器对数据进行移位和比较,如果判断是带有头文件标志的数据,那么数据将被接收,否则不接收。通过内部计数器计数得到想要的数据量后再次判断和比较,进入下一轮的数据接收,接收到的串行数据经内部转换变成并行数据送给FIFO,经VB软件读数,将其显示在电脑上。主题内容就是烧写计数器,移位寄存器,串转并的功能到CPLD中,经过编译来对发数装置的数据进行仿真分析后验证其正确性,再将数据传入先进先出的FIFO,最后通过USB将数据传出 ,由电源电路对整个过程供电。

设计特点

本设计采用CPLD为核心的设计方案,利用CPLD的优点,实现了高集成度的设计特点,把位移寄存器,计数器 串行信号转化并行信号的功能都烧写在了CPLD上。把并交给了先进先出存储器以此来实现数据传输的功能。并没有采用单片机,这样的设计减小了物体的体积,减小了功率消耗,实现了高度的集成。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0166,word全文:36页,合计:8200字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于CPLD的数据判断及传输模块的设计(开题报告,任务书,论文)!

当前位置:

当前位置: