基于CPLD的QPSK调制器电路设计

[关键词:CPLD,QPSK,调制器] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0297,word全文:33页,合计:11000字 |

本文根据QPSK调制与解调的基本原理,给予FPGA实现QPSK调制与解调电路的设计。

论文内容

本论文讨论了QPSK调制的方法,介绍了QPSK调制的基本原理,描述了整体电路的规划和具体分析了电路中各个模块的组成和作用;并利用CPLD技术实现QPSK调制器;最后对实际电路进行了调试测试。

CPLD技术正日益广泛地应用与现代通信的各个领域。本设计中采用的是Altera公司生产的引脚为44脚的CPLD芯片EPM7064SLC44-10,具有芯片集成度高、内部资源丰富、用户可用引脚多等显著优点,不易出现芯片内部资源尚有空余而芯片引脚已用完的情况。在本设计中,该芯片与外围电路配合,在一块简单的电路板上便可以实现基带信号的QPSK调制。只需要下载不同的程序到电路板上,便可以实现不同的功能。

宏单元(macrocells)

逻辑阵列块LAB是MAX7000S系列中具体的逻辑单元,用来实现各种具体的逻辑功能。宏单元由逻辑阵列,乘积项选择矩阵和可编程触发器构成

......

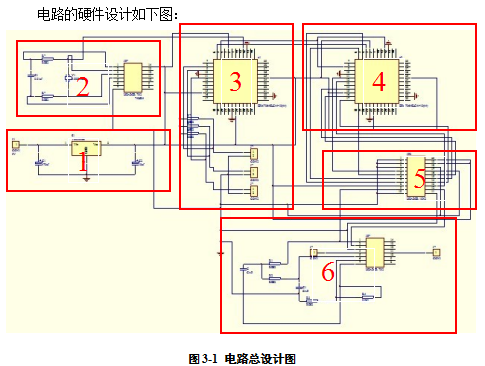

系统电路总体由6个模块组成,其中有电源模块,时钟信号模块,基带信号发生模块,调制模块,D/A转换模块,滤波模块。

电源模块为其他各个模块提供一个5V的电压,时钟信号产生了一个4MHz的时钟,基带信号发生模块产生了0码,1码,0/1码,以及各种M序列。调制模块将基带信号调制成8位抽样信号输出,接着经过D/A模块转换成模拟信号,最后经过滤波模块输出最后的较清晰地信号。

电路总共分为6大部分

第一部分为电源电路,提供一个5V的电压;

第二部分为时钟信号电路,产生了一个4MHz的时钟;

第三部分为基带信号发生模块,产生了0码,1码,0/1码,以及各种M序列;

第四部分为调制模块,将基带信号调制成抽样信号输出;

第五部分为D/A模块,作用是将调制模块输出的信号转换成模拟信号;

第六部分为滤波模块,模拟信号经过滤波后完成模拟信号重建。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0297,word全文:33页,合计:11000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于CPLD的QPSK调制器电路设计(论文)!

当前位置:

当前位置: