基于单片机与CPLD的等精度频率计的设计

[关键词:单片机,CPLD,频率计] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文,答辩稿】 作品编号:ckjs0256,word全文:36页,合计:22000字 |

本课题研究问题

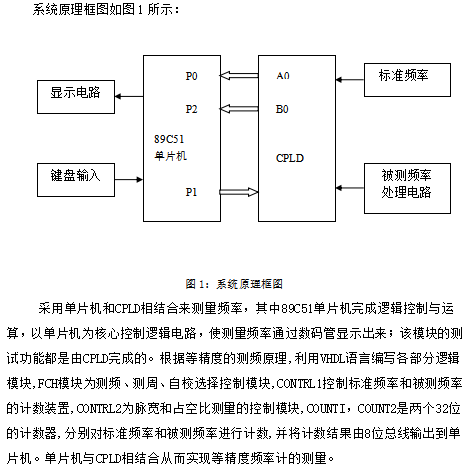

采用单片机与CPLD相结合实现对频率的等精度测量,其中频率的测量范围为1-100MHz,由于门信号的宽度Tc 改变以及随机的出现时间造成的误差最多只有基准时钟B-CLK 信号的一个时钟周期, 由于B-CLK 的信号是由高稳定度的100MHz 晶体振荡器发出的,所以任何时刻的绝对测量误差只有有10-8s,这也是系统产生主要的误差,也是CPLD测量达到的精度。

本文论述了数字频率计的实现,利用CPLD(Complex Programmable Logic Device)进行频率的计数,单片机实施控制实现频率计的设计过程。该频率计利用CPLD来实现频率、周期、脉宽和占空比的测量计数。等精度的测量方法具有较高的测量精度。利用单片机完成整个测量电路的测试控制、数据处理和显示输出。

本文论述了硬件电路的组成和单片机的软件控制流程。其中硬件电路包括按键控制模块、显示模块、输入信号的放大整形模块以及单片机和CPLD主控模块。系统将单片机89C51的控制灵活性及CPLD芯片的现场可编程性相结合,不但大大的缩短了开发研制的周期,而且还使本系统具有结构紧凑、体积小,可靠性高,测量范围广、精度高等优点。

结语

等精度的测量方法不但具有较高的测量精度,而且在整个频率区域保持恒定的测试精度。该频率计利用等精度的设计方法,克服了基于传统测频原理的频率计的测量精度随被测信号频率的下降而降低的缺点。本频率计使用高速CPLD芯片来构成主要逻辑模块,完成该等精度频率计主控程序设计,实现对频率变化范围较大的信号进行频率测量。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文,答辩稿】 作品编号:ckjs0256,word全文:36页,合计:22000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于单片机与CPLD的等精度频率计的设计(开题报告,任务书,论文,答辩稿)!

当前位置:

当前位置: