基于CPLD的扰码解扰器设计

[关键词:CPLD,扰码解扰器] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0298,word全文:36页,合计:10000字 |

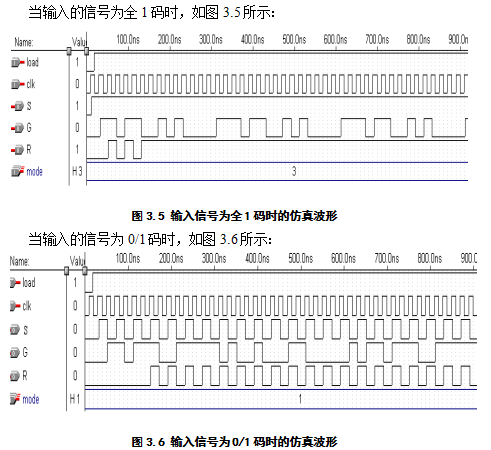

本论文介绍了数字通信中的扰码和解扰原理,利用CPLD芯片进行扰码器和解扰器设计。将通过MAX+plus II软件得到的仿真图形和用示波器对电路板调试所得到的波形进行比较,验证本设计的正确性。此本设计所研究的内容对通信原理实验的扩展非常有意义,具有较高的实用价值。

我的主要工作为:

1.查阅相关文献,了解扰码和解扰原理及m序列原理;

2.在MAX+plus II编译环境下,用VHDL语言进行扰码器和解码器的编程,编译以及调试,直至仿真通过;

3.选择ALTERA EPM7064SLC-44芯片,进行管脚配置,并且将相关的程序下载到CPLD元器件上;

4.最后在焊接好的电路板上进行调试,利用示波器分析验证结论。

仿真步骤

1.进入系统后,单击“开始”\“程序”\“MAX+PLUS II”进入。

2.建立新的文本文件。选取菜单项MAX+PLUS II\Text Editor或菜单项File\New,也可以用鼠标单击工具栏中的图标,在弹出的对话框File Type中选择Text Editor file,按OK后就开始编辑文本文件。

3.保存文件。将所设计好的程序输入文本编辑框后,选菜单File\Save,在弹出的Save As 窗口中,设定好存放目录和文件名后,按OK便可(这里有二个注意点:第一,存放的目录不可以是中文;第二,保存的文件名应该与程序的文件名一致,不然,编译将不能通过)。

4.选择芯片。选择MAX+PLUS II\Assign菜单,选中Device,选择相应的芯片,本次设计选择的是ALTER EPM7064SLC-44-10芯片。

5.编译文件。在编译之前,先要设定总时钟长度, 选择File\End Time菜单,这里我们设置为1.0us,然后,输入时间间隔,选择Options\......

本设计应用 CPLD芯片完成了扰码器和解扰器系统的设计。以MAX+plusⅡ为程序运行工具,利用VHDL语言编程并烧录到EPM7064SLC44-10芯片上实现功能。在硬件设计方面,利用Protel99SE设计电路原理图。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0298,word全文:36页,合计:10000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于CPLD的扰码解扰器设计(论文)!

当前位置:

当前位置: