基于CPLD的信号采集系统研究

[关键词:CPLD,信号采集系统] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0299,word全文:45页,合计:13000字 |

本文研究的内容是以CPLD为控制核心,利用VHDL语言在Quartus II环境下编程,AD模数转换器进行数据采集。系统具有32路信号通道,输入输出各16通道,通过模拟开关进行通道选择,AD采样75KHZ信号,信号数据最终由CPLD进行处理。

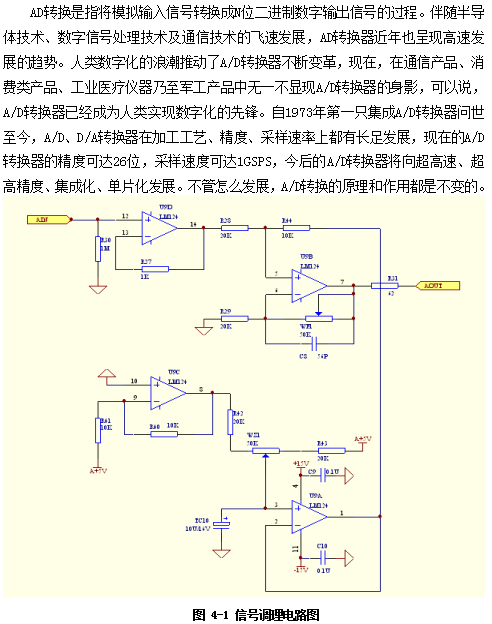

传感器信号通常是微弱的小信号,在工业现场的信号通常是受到干扰的信号,这就需要对信号进行条理,包括信号放大、滤波、相位调整、幅值调整等步骤。利用VHDL语言编程,将要实现的各种功能模块化,可以单独运行,最终合成具有功能意义的整体系统。

系统设计概述

本方案设计分为硬件总体方案设计和软件总体方案设计。前者将对采集的原理及各组成电路的功能进行大致的描述。后者将描述采集驱动程序的功能及其方案设计。

研究内容及主要技术指标

研究内容

本课题内容为基于PCI总线的高速模拟信号采集卡研制。采集卡具备以下三个主要功能:

1.模拟信号通道控制;

2.模拟信号调理;

3.AD转换控制。

本系统基于CPLD集成控制,拥有32路模拟信号输入端口。它的总体框图如图3-1所示。图中AIN0、AIN1……AIN30、AIN31表示32路模拟输入信号,CPLD通过四个模拟开关控制选通通道。

在本卡的模拟信号采集通道中,信号调理电路对模拟输入信号进行幅值调整后,将其送入AD模拟信号入口。32路AD在时钟信号的同步下进行模数转换。由AD输出的数字信号由CPLD处理。

软件总体方案设计

本系统以CPLD为控制中心,运用VHDL语言编程,在Quartus II 7.0环境下开发。主要实现AD的读写控制,和通道的选择控制。

本程序实现的功能有:

1,控制32路模拟开关,选择采集通道。

2,对12M晶振进行10分频做为AD时钟信号。

3,控制AD读写,采集数字信号。

在需要采集多路模拟信号、开关信号、频率(计数)信号等的数据采集应用中,利用通用板卡构成计算机测控系统是可行的,但对于产品的批量应用,其成本与综合性能不能令人满意。技术成熟的CPLD芯片的应用,可以很好地将逻辑控制、数据信号处理等功能集于一身,使以往需要利用多块信号板卡才能完成的任务整合于同一采集控制器中,从而有效地提高控制系统的可靠性,降低测控系统的实现成本。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0299,word全文:45页,合计:13000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于CPLD的信号采集系统研究(论文)!

当前位置:

当前位置: