QPSK调制与解调模块研究

[关键词:QPSK,调制解调] [热度 ]| 提示:此毕业设计论文完整版包含【论文,源程序】 作品编号:txgc0083,word全文:39页,合计:20000字 |

本设计主要包括两个部分:调制部分、解调部分。两者为实现同步,必须要有频率相同的载波信号。在本设计中调制和解调主要是由芯片实现其功能,因此,关键是载波信号的得到,既由琐相环控制的压控振荡器。本设计采用高精确跟踪的琐相环控制芯片外接VCO,可达到两部分的载波频率相等,这样就能满足相干解调的要求。下图为本设计的整体信号流图。

电路原理分析

在本设计中,主要采用琐相环得到高稳定的频率源。该部分是设计的重点也是难点之一,按要求需要35MHz-70MHz的载波信号,但有与MAX2451和MAX2452内部需要对载波进行二分频电路产生正交载波信号,所以实际需要的外部振荡频率是70MHz-140MHz的载波信号,由于琐相环电路具有高跟踪性能和高精确度,通过琐相环控制VCO可产生稳定精确的所需频率信号。下图2-10为本设计中锁相环控制的基本原理

......

由图2-10可以看到:本芯片主要是实现标准频率和输入频率的鉴相,由CE、CK、DA控制芯片的分频比N、标准频率的选择和工作状态。当输入频率信号(FMIN、AMIN、IFIN)经过N分频后,和标准频率(有本振经过预分频REFERENGE DIVIDER输出)进行鉴相的鉴相输出PD。本芯片的关键是要得到正确的串行控制字CK,CE,DA。

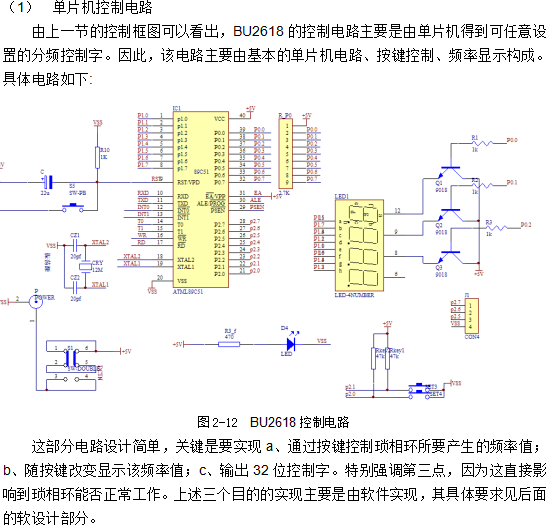

利用锁相环路法构成数字式频率合成器,应用BU2618内部的数字逻辑电路把压控振荡器VCO频率一次或多次降频至鉴相器频率上,再与参考频率在鉴相电路中进行比较,所产生的误差信号用来控制VCO的频率,使之锁定在芯片内参考频率的稳定度上。

通过单片机89S52的P1口对BU 2618的CE,CK,DA 信号口进行控制,采用串行写入以确定BU2618的工作方式和分频比。其具体的写入方式和要求见后面的软件设计部分。另外在BU2614/BU2618,含有一个鉴相器。鉴相器(PD)又称为相位比较器,它对输入信号vi(t)与压控振荡器(VCO)输出信号vo(t)的相位进行比较,产生误差电压vd(t);环路滤波器(LF)的作用是滤除误差电压vd(t)的高频成分和噪声,并且能改善锁相环的噪声性能;压控振荡器的振荡频率将受环路滤波器输出电压控制,使其输出信号fo与环路的输入信号fi的频率和相位差减小直至锁定。在锁相环路正常工作时,输出信号的频率fo与输入信号的频率fi相等,并且相位差为常数,该相位差维持着两信号的同步,使输出信号频率稳定。

从图3-2可以看出,对同一个基带信号,按向量差和相位差回出的DPSK波形是不同的但是如果TB是载波周期Tc整数倍时,按照上述规定作图,结果发现,向量差和相位差对应的DPSK波形完全相同(见下图3-3)。最后再说明一点,在图中,第一个码元的波形是任意假设的,若假设的码元波形与图中反相,根据定义也可画出DPSK波形,此波形虽然与图示波形不同,但是它们代表的基带信号却是相同的。

从两图中可以看出,2DPSK也可以是另一符号序列(见图中下部的序列,称相对码)经绝对移相而形成的。这说明,一方面,只有已知移相键控方式是绝对的还是相对的,才能正确判定原信息;另一方面,相对移相信号可以看作是把数字信息序列(绝对码)变换成相对码,然后在根据相对码进行绝对移相而形成的。

序列信号发生电路

根据设计要求,需要得到两路正交串行数据同时输入MAX2452芯片,这两路数据的输出由单片机AT89S52读取16位拨码信号,控制分为两路间隔输出。其电路图如下所示,在这个电路中,我们主要是产生两路单极性序列,高电平电压为5V。根据后面调制原理的介绍,要求调制序列为双极性,因此,这是我们需要特别注意的一个问题。另外,对于美信系列的上述芯片,工作电平为3V,输入序列电压要求不超过1.75V,因此,我们还必须注意电平的转换,这两个内容的改进具体在后面调制解调电路部分说明。

| 提示:此毕业设计论文完整版包含【论文,源程序】 作品编号:txgc0083,word全文:39页,合计:20000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——QPSK调制与解调模块研究(论文,源程序)!

当前位置:

当前位置: