基于CPLD数字频率计的设计

[关键词:CPLD,数字频率计] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0479,word全文:36页,合计:14000字 |

要研究的部分

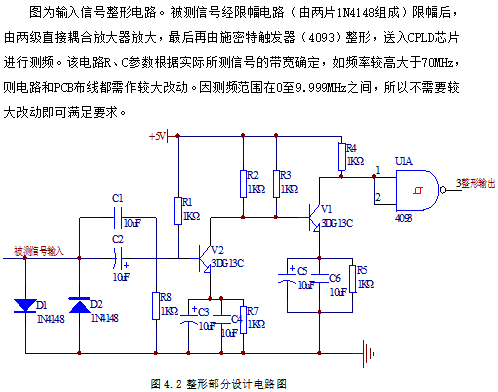

数字频率计是一种用数字显示的频率测量仪表,它不仅可以测量正弦信号、方波信号的频率,还可以测量如机械振动次数、物体转动次数、单位时间里经过传送带的产品数量等多种物理量。

本设计主要论述了利用CPLD实现多功能频率计的过程,使得频率计具有了测量精度高、功能丰富、控制灵活等特点。该频率计按照直接测频法、等精度测频法的原理,克服了传统技术中测频精度随被测信号频率下降而下降的缺点。两种测量方法测量均具有较高的测量精度。

设计思路为采用现场可编程门阵列为控制核心,利用VHDL语言编程,下载烧制实现。将所有器件集成在一块芯片上,体积大大减小的同时还提高了稳定性,可实现大规模和超大规模的集成电路,测频测量精度高,测量频率范围大,而且编程灵活、调试方便。

众所周知,频率信号易于传输,抗干扰性强,可以获得较好的测量精度。因此,频率检测室电子测量领域最基本的测量之一。频率计的基本原理是用一个频率稳定度高的频率作为基准时钟,对比测量其他信号的频率。通常情况下计算每秒内待测信号的脉冲个数,即闸门时间为1s,闸门时间可以根据需要取值,大于或者小于1s都可以。闸门时间越长,得到的频率值就越准确,但闸门时间越长,则每测一次频率的间隔就越长,闸门时间越短,测得的频率值刷新就越快,但测得的频率精度就受影响,一般取1s作为闸门时间。

本设计用两种方法实现测频,第一种是直接测频法。所设计的频率计基本测量原理是,首先用频率稳定的标准信号产生闸门信号,并在一定的闸门时间内,用计数器计算待测信号脉冲的个数,把标准时间内的计数的结果,用锁存器锁存起来,最后用显示译码器,把锁存的结果用LED数码显示管显示出来。

本课题要求毕业生设计一套基于CPLD数字频率计系统。

1测量频率小于100KHz。

2被测信号小于3V的交流正弦信号。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0479,word全文:36页,合计:14000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于CPLD数字频率计的设计(开题报告,任务书,论文)!

当前位置:

当前位置: