基于FPGA的O-QPSK调制解调器设计

[关键词:FPGA,O-QPSK,调制解调器] [热度 ]| 提示:此毕业设计论文完整版包含【论文,源程序】 作品编号:txgc0315,word全文:70页,合计:20000字 |

本设计基于Simulink、Quartus II、ModelSim等软件平台,用硬件描述语言完成了偏移正交相移键控调制解调系统各个模块和总体系统的设计,并在现场可编程门阵列开发板上实现该系统的功能。本设计具有无码间串扰、功率谱旁瓣低、有较高的频谱利用率和功率利用率,以及实现方法简单、开发周期短、集成度高、处理速度快、体积小和软件可升级等优点。本设计是采用一种新的方法来实现偏移正交相移键控的调制,对调制技术的研究提供了一种新思路,具有一定的理论研究价值,对我国通信技术中的高速调制技术的发展具有一定的意义。

本论文的主要工作包括:

(1)完成课题研究的背景调研,了解课题研究现状;

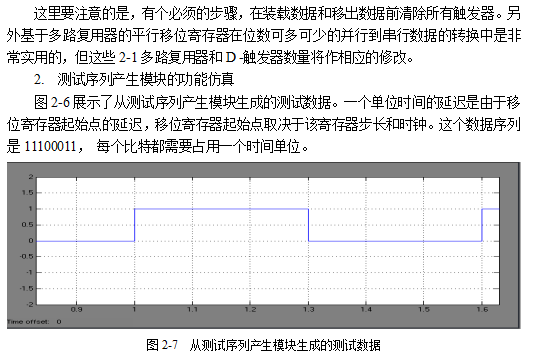

(2)研究OQPSK数字调制解调的基本原理,并在Matlab/Sinmulink平台上构建出基于FPGA的OQPSK调制解调系统的各模块方案和总体方案,并用Simulink对系统进行功能仿真;

(3)在Quartus II软件开发平台上,用硬件描述语言设计各调制解调模块;并对各模块系统的功能进行仿真,验证调制解调器各个模块功能的正确性和可靠性;完成基于FPGA器件的OQPSK通信系统的综合设计;并对整个系统的功能进行仿真验证和时序验证;

(4)在实验室己有的FPGA硬件平台上,实际测试已完成设计的正确性和性能。

本论文的主要内容安排如下:

第1章: 绪论。主要介绍课题的研究背景,课题在国内外的发展状况,以及本课题的研究意义和本论文将要研究的内容。

第2章:OQPSK调制解调的Simulink仿真设计和功能仿真。主要介绍在Matlab/Simulink平台上构建出OQPSK调制解调系统的各模块方案和总体方案,并用Simulink对系统进行功能仿真。

第3章: OQPSK调制解调器发射端的Verilog HDL实现和时序仿真。这一章的任务是在Quartus II软件开发平台上,用硬件描述语言(Verilog HDL)设计发射端各模块,包括测试数据产生模块,数据分流模块,时钟分频模块,调制模块等。

第4章: OQPSK调制解调器接收端模块设计和时序仿真。这一章的任务是在Quartus II软件开发平台上,用硬件描述语言(Verilog HDL)设计接收端各模块,包括混频模块,低通滤波模块等,最后完成OQPSK通信系统的综合设计,并完成各个模块和OQPSK通信系统的综合仿真,验证各个模块和综合系统的功能的正确性和可靠性。

第5章: OQPSK调制解调系统的硬件实现。这一章将把整个OQPSK调制解调系统写入到EP2C35F672C6芯片里,在DE2开发平台上,实际测试已完成设计的正确性和性能。

最后对本论文的所有工作做一个全面的总结和展望。

本论文提出了一种比较简单的方法来实现OQPSK的调制解调,也特别详细介绍了OQPSK调制解调的原理,简要的说,即通过载波相移去代表要传输的位对,然后再在接受端通过判断载波的相移把被传输的位对识别出来,本论文说明了像OQPSK那么复杂的调制方式,也可以用简单的模块来实现,以避免其复杂的数学块运算。这个简单的方法也可以推广到OQPSK调制解调的模拟硬件的实现中去。

本论文的主要工作是构建了OQPSK调制解调的总体方案,并用Matlab/Simulink对系统的功能进行了仿真,然后再用Verilog HDL对各个模块进行设计,其中主要包括二进制序列产生器模块的设计,串并转换模块的设计,载波发生器模块的设计、低通滤波器模块的设计、调制和解调综合模块的设计,并在此基础上完成了基于FPGA实现的OQPSK系统的调制解调器的仿真。从整个系统联合仿真的波形看出,二进制序列发生器产生出来的数据输入到系统的调制端,然后在解调端能正确解调出数据,实现了OQPSK的调制解调。

| 提示:此毕业设计论文完整版包含【论文,源程序】 作品编号:txgc0315,word全文:70页,合计:20000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于FPGA的O-QPSK调制解调器设计(论文,源程序)!

当前位置:

当前位置: