基于FPGA的UART接口设计

[关键词:FPGA,UART] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文,答辩稿】 作品编号:ckjs0217,word全文:40页,合计:15000字 |

本课题要求设计基于FPGA的UART接口,工作内容如下:

1.查阅相关文献不少于30篇;

2.采用VHDL进行描述,编写软核代码;

3.可编程的波特率发生器模块、计接收器模块和发送器模块、8字节FIFO模块;

4.11位UART。串行数据格式:串行数据包括8位数据、1位起始位(start bit)、1位结束位、1位校验位;

5.综合仿真。

论文的主要研究工作

1.硬件设计方面:设计本系统的原理图,包括可编程的波特率发生器模块、计接收器模块和发送器模块、8字节FIFO模块。

2.软件设计方面:在FPGA中实现了基于VHDL的逻辑控制,实现串行数据包括8位数据、1位起始位(start bit)、1位结束位、1位校验位的系统要求,并在MAX PLUS II的环境下实现了功能和时序仿真。

3. 查阅相关文献,了解此课题的相关理论知识。

论文的结构安排

论文的结构安排如下:

第一章:介绍了本课题的背景、意义和国内外发展现状。

第二章:介绍了基于FPGA的UART接口设计的整体设计方案,及各个模块的功能设计和原理图。

第三章:对系统逻辑设计进行了说明,介绍了端口初始化合模块设计流程。

第四章:介绍了本设计的调试过程,并简单的介绍了姿态过载的模型计算并。

第五章:针对本次设计内容做出了结论和展望。

结论

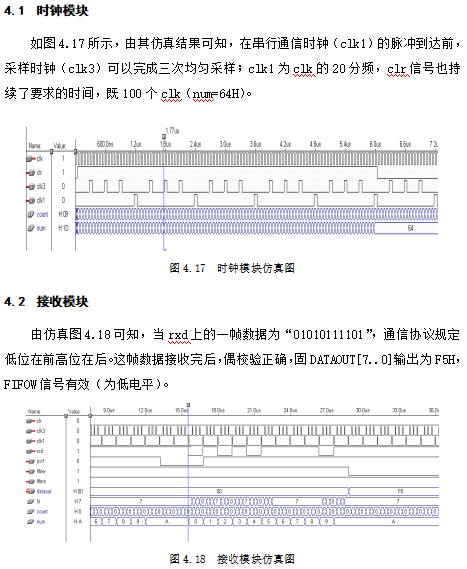

本设计完成的是基于FPGA的异步串行通信电路的设计,包括硬件电路设计与程序设计。电路能够以串行异步工作方式发送数据和接收的数据,能够进行奇偶校验。异步接收和发送电路集成在FPGA中,电路能够响应计算机向平台发送的实时监测命令。当接收数据出错时,能够重新接收数据。为了减少数据传输误码率,除了设置奇偶校验位,还设置了三倍频于系统时钟的采样时钟。通过程序的仿真及最终电路的调试,验证了该异步串行通信系统达到了技术要求。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文,答辩稿】 作品编号:ckjs0217,word全文:40页,合计:15000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于FPGA的UART接口设计(开题报告,任务书,论文,答辩稿)!

当前位置:

当前位置: