基于FPGA的CRC校验码的实现

[关键词:FPGA,CRC,校验码] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文,答辩稿】 作品编号:ckjs0215,word全文:30页,合计:11000字 |

主要研究和解决的问题

设计一个CRC模块,该模块可以准确计算输入的若干位数据的CRC校验码,根据电路中各移位寄存器的不同状态值,推导出8位并行计算的CRC的逻辑关系式。在发送方根据要传送的K位信息码,以一定的规则产生一个校验用的监督CRC码r位,并附在信息后边,构成一个新的二进制码序列数共k+r位,最后发送出去。在接受方则根据信息码和CRC码之间所循环的滚则进行检验,已确定传送中是否出错。

本课题完成的工作及研究内容

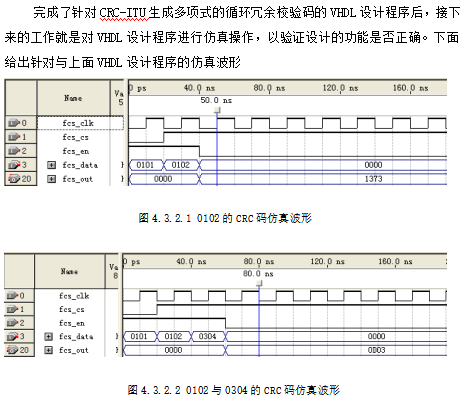

设计CRC模块,该模块可以准确计算输入的若干位数据的CRC校验码,根据电路中各移位寄存器的不同状态值,推导出16位串/并行计算的CRC的逻辑关系式。在发送方根据要传送的K位信息码,以一定的规则产生一个校验用的监督CRC码r位,并附在信息后边,构成一个新的二进制码序列数共k+r位,最后发送出去。在接受方则根据信息码和CRC码之间所循环的滚则进行检验,已确定传送中是否出错。主要流程为第二章介绍CAN总线的基本特点和构成,第三章主要探讨CRC的校验原理,第四章进行CRC的具体设计,第五章对设计CRC模块进行硬件调试。

总结

本文在分析了CRC计算原理的基础上,仔细运用VHDL的特点进行串、并行CRC算法建模从而实现的设计,不仅具备采用公式法设计所具有的优点,还能很好地适用于各种数据块大小不同、生成多项式选取不同的CRC编/解码运用场合,明显减轻设计开发工作量,大幅缩短产品的研发周期。此外,由于生成结果占用的硬件资源很少,只需利用系统集成芯片中剩余的少量资源即可实现,在当前大量的系统设计实现趋向单芯片化的大潮下,更具生命力。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文,答辩稿】 作品编号:ckjs0215,word全文:30页,合计:11000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于FPGA的CRC校验码的实现(开题报告,任务书,论文,答辩稿)!

当前位置:

当前位置: