基于FPGA的CRC编解码电路的设计

[关键词:FPGA,CRC,编解码] [热度 ]| 提示:此毕业设计论文完整版包含【论文,答辩稿】 作品编号:txgc0314,word全文:28页,合计:9600字 |

本文首先对CRC编码和解码的基本原理进行了分析,然后详细讨论了CRC编解码电路的原理及设计方案,最后采用VHDL语言完成了CRC的编码和解码以及模拟信道程序设计,并在QuartusⅡ软件平台进行仿真分析,仿真结果表明,设计符合要求。

本文第一章介绍了VHDL语言、FPGA技术和QUARTUS II开发平台;第二章介绍了CRC编解码的基本原理、编码方法以及解码方法;第三章详细分析了基于FPGA的CRC编解码电路的设计流程以及仿真电路分析;第四章是对设计的全面总结。

本文探讨的是基于FPGA的CRC编解码电路的设计。本章是设计平台的介绍,第一节介绍VHDL硬件电路描述语言,第二节介绍FPGA技术,第三节介绍Quartus II软件设计平台。VHDL语言简单易懂,易于编写。FPGA技术运算速度快,可进行大规模的复杂运算。最重要的是,Quartus II设计平台支持多种语言的操作,可将复杂的电路简单化。因此,采用VHDL硬件电路描述语言对电路功能进行描述,基于Quartus II软件设计平台完成本设计的全部要求。

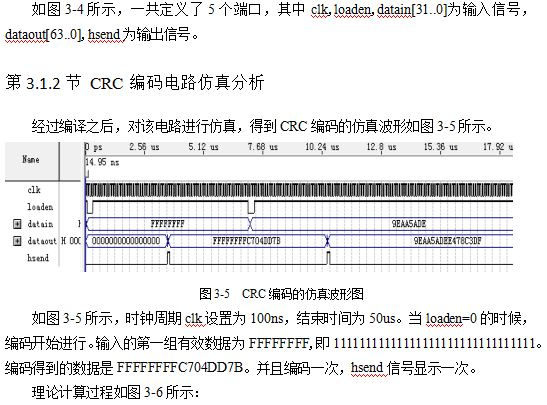

仿真结果如图3-15所示,设置时钟clk为100ns,结束时间为50us。使能信号loaden为0的时候开始工作。设置模拟信道中的a的值为00,即传输的过程中无噪声干扰,输入的第一组数据为FFFFFFFF,得到的解码结果也是FFFFFFFF。输入的第二组数据为9EAA5ADE,得到的解码结果 也是9EAA5ADE。同时,这两组数据的correct都为1,error为0,表示这两组数据编码正确。由图3-5、3-11可知,这两组数据编解码正确。

......

仿真结果如图3-18所示,设置时钟clk为100ns,结束时间为50us。使能信号loaden为0的时候开始工作。设置模拟信道中的a的值为11,即传输的过程中有噪声干扰,并且信息码和冗余码的位置均出现错误。输入的第一组数据为FFFFFFFF,解码后得到的数据是FFFFFFFE。输入的第二组数据为9EAA5ADE,解码后得到的数据为9EAA5ADF。显然,这两组数据的编解码是错误的。并且error为1,correct为0也表示这两组数据的编解码是错误的。

通过以上的仿真验证,表明程序设计正确,达到了设计的要求。完成了发送方发送32位数据,经过编码得到64位的编码数据,再将64位的编码数据通过模拟信道,最后,接收方能够对64位编码数据进行解码,并且判断解码是否正确的功能。

......

本次设计是基于FPGA的CRC编解码电路的设计,采用的生成多项式是CRC-32。在设计电路的过程中,将整个电路分成了三个部分。第一部分是CRC的编码模块,可将要发送的数据进行CRC的编码。第二部分是模拟信道模块,它起到的作用相当于是对发送的数据进行噪声干扰,最后得到的数据可能发生了误码。第三部分是CRC解码模块,是把从模拟信道传输过来的数据进行解码,如果解码错误则有error信号提示解码出错。这样,接收方就能正确判断接收的数据是否正确,可以有效地提高信息传输的正确度。经过系统电路验证,表明设计正确。

本设计是用VHDL语言编写的,VHDL语言的功能强大、设计比较灵活、易于修改并且系统的硬件描述能力强。编写程序的时候易于理解,操作简单。利用Quartus II可以使复杂的电路设计变得简单化,降低了设计成本,缩短了设计周期。

| 提示:此毕业设计论文完整版包含【论文,答辩稿】 作品编号:txgc0314,word全文:28页,合计:9600字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于FPGA的CRC编解码电路的设计(论文,答辩稿)!

当前位置:

当前位置: