FPGA在串行传输技术中的应用

[关键词:FPGA,串行传输] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0162,word全文:30页,合计:14000字 |

论文的研究内容和结构安排

本论文是基于FPGA开发板,对研究串行通讯过程中软、硬件设计遇到的问题加以总结归纳,提高系统运行效率。主要研究了在FPGA实现低压差分串行传输过程。论文结构安排如下:

第一章 绪论介绍了课题研究的背景,国内外研究现状及发展趋势。

第二章 介绍设计的总体设计思路及LVDS技术,设计接口流程图及相应的控制电路。

第三章 介绍设计工具。

第四章 毕业设计的结论。

本课题需要研究和解决的问题

本课题需要研究基于FPGA的低压差分信号的串行传输技术,了解FPGA的工作原理,低压差分串行传输技术;同时解决了数据的并串转换及串并转换,以实现数据的高速远距离的传输。

本课题拟采用的研究手段(途径)

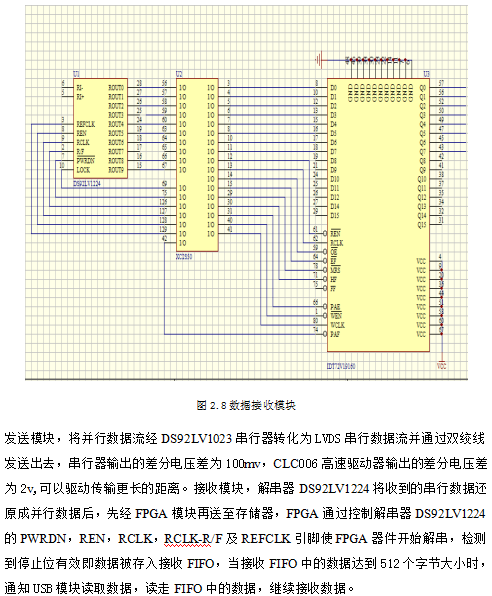

本课题研究基于FPGA的低压差分串行传输技术来实现数据的传输。由于在PC机内部和DSP很多数据是并行传输的,因此重点是需要在发送方向和接收方向有数据的并串转换模块和串并转换模块,将LVDS长线传输模块分为LVDS发送电路和LVDS接收电路,其中串行器将接收到的数据转换成LVDS串行数据流并发送出去,而解串器是将LVDS串行数据还原成并行数据流的。实现数据的高速远距离传输。其中,FPGA是控制平台和发送接收终端。FPGA传输采集后的数据,并通过USB接口送至PC机。

设计方案

在DSP或者PC机内部数据是高速并行传输的,因此本设计中用FPGA来实现异步串行数据传输时,重点是需要在发送方向和接收方向必须有数据并串转换模块以及串并转换模块,以将高速并行数据流转换成串行数据流,再将串行数据流转换成并行数据流。DS92LV1023和DS92LV1224是美国国家半导体公司推出的10位总线型低压差分信号的应用芯片组。其中DS92LV1023是可将10位并行CMOS或TTL数据转换为具有内嵌时钟的高速串行差分数据流,并通过双绞线发送;而DS92LV1224则是接收该差分数据流还原成并行数据的解串器,它同时又可以重建并行时钟。采用该器件组进行数据串化时采用的是内嵌时钟,这样可有效地解决由于时钟与数据的不严格同步而制约高速传输的瓶颈问题。数据采集和LVDS器件接口的时序匹配问题则选用FPGA来实现。

本设计是主要对复杂的可编程逻辑器件FPGA进行设计,以实现数据的低压差分串行传输。通过本次设计我对复杂可编程逻辑器件FPGA有了较深刻的认识,熟悉所要设计电路中整个电路的功能原理,对各个模块的功能与作用有了一定的了解,体会到了用FPGA设计电路的许多优点,并用FPGA实现了对LVDS接口时序的匹配,懂得了如何根据要求来设计一个完整的电路;设计出了发送电路模块和接收电路模块,懂得了理论实践相结合的重要性,和它们之间的距离,只有真正的去实践了,才能更深刻的理解理论。本次设计采用ProtelSE99来绘制LVDS接口的电路原理图。使我对Protel 99 SE原理图有了更加深入的了解与掌握。善于思考,敢于尝试,勇于创新,提高解决问题的能力。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0162,word全文:30页,合计:14000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——FPGA在串行传输技术中的应用(开题报告,任务书,论文)!

当前位置:

当前位置: