基于FPGA多通道采样系统设计

[关键词:FPGA,多通道,采样系统] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:ckjs0569,word全文:45页,合计:24000字 |

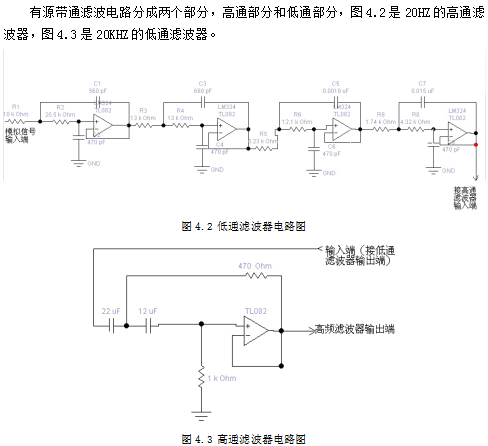

本次设计采用FPGA实现采样系统,从而系统具有高速、稳定、低功耗等特点,音频模拟信号经放大器NE5532放大后,经过8路选择后,进入滤波器进行滤波,滤掉高频干扰信号和低频干扰信号的干扰,然后进入AD7892进行AD采样,采样后的12位数据通过一个FIFO队列存储,最后从FIFO中读出数字信号,在串并输出模式的选择下在示波器上显示出来。

本系统硬件电路包括FPGA设计的多通道采样控制器和相应的通道选择电路,A/D转换电路,由于采样音频信号,所以需要设计音频的放大和滤波电路。

方案一

用FPGA实现一个3位8进制的计数器,记数脉冲是FPGA锁存AD转换数据的锁存信号,计数器的输出作为数据开关CD4051的地址。利用进程的并行操作来实现AD574来实现AD转换,这个方案的优点是节省了FPGA芯片的资源,但数字电路较为复杂,而且AD574的转换速率最高达到50KHz,不能达到8通道的高速音频采集。

方案二

用FPGA实现一个3位8进制的计数器,记数脉冲是FPGA锁存AD转换数据的锁存信号,计数器的输出作为数据开关CD4051的地址。用有限状态机来实现对AD7892的控制,用外部RAM实现采样数据的存储,这样电路实现比较简单,而且AD7892的采样速率可以达到500KHz,可以实现8个通道同时8路音频信号采集。但需要外接RAM芯片,成本比较高,而且外部RAM的读写速度达不到高速数据采集的要求。

方案三

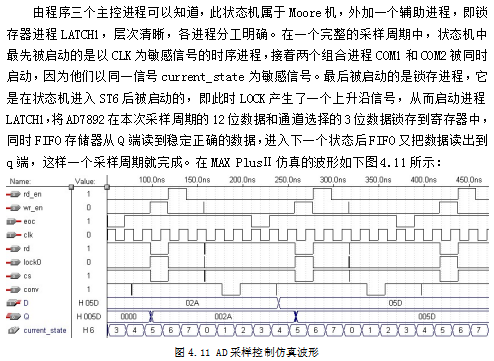

用FPGA实现一个3位8进制的计数器,记数脉冲是FPGA锁存AD转换数据的锁存信号,计数器的输出作为数据开关CD4051的地址。用有限状态机来实现对AD7892的控制,这样电路实现比较简单,而且AD7892的采样速率可以达到500KHz,可以实现8个通道同时8路音频信号采集。同时采用FIFO模块,让数字数据先存到队列中,一边往队列中写数据,一边从队列中读数据,这样就对数字数据起了一个高速缓存的作用,更加快了整个系统的运行速度。

方案比较

为获得更佳的系统功能,使系统资源能得到充分地利用,我们采用第三种方案。主要是因为状态机容易构成性能良好的同步时序逻辑模块,为了消除电路中的毛刺现象,在状态机设计中有很多种设计方案可供选择。FIFO队列的读写操作只需要一个周期就可以完成,起到高速缓存的作用,这样更加快了整个系统的运行速度,解决了采样和存储的“瓶颈问题”,更加有效地利用FPGA芯片的资源。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:ckjs0569,word全文:45页,合计:24000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于FPGA多通道采样系统设计(论文)!

当前位置:

当前位置: