基于FPGA的时分多路复用设计实现

[关键词:FPGA,时分多路复用] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc1003,word全文:27页,合计:8800字 |

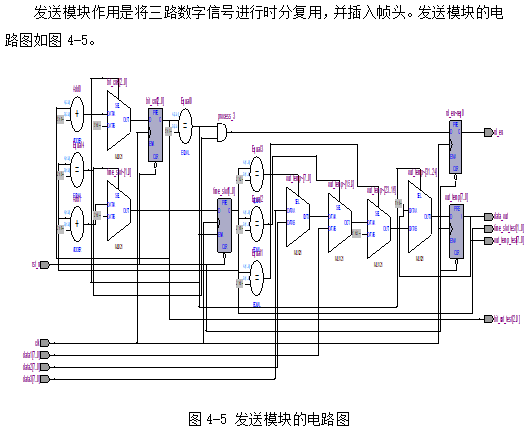

本文主要设计的是一个利用FPGA技术来仿真实现的时分多路复用系统。设计的时分多路复用系统的作用主要是将三路编码自动生成的8-bit信号数据由FPGA对其进行时分复用,通过信道传输,再由收端恢复出原本的三路信号数据。本篇论文详细阐述了时分多路复用系统的设计方法,制作过程,以及过程中所遇到的问题。在本次的设计工作中,构建系统各部分电路元件的系统框图和原理图,之后根据原理图设计代码,然后在QuartusⅡ 9.1上运用VDHL语言进行代码编程,最后通过仿真将设计实现。

......

位同步原理

本文的时分多路复用系统中最基本的同步就是位同步了。它是作为帧同步实现的前提。位同步的主要目的是区分码元,令收端所得一定的码元序列,而这些码元序列都代表着一些信息。位同步要求收端的频率和相位要和发端一致,也只有这样,收端才能保证的接收和判断信道传输过来的发端的码元是正确的。故此,为了收端能够确定判决时刻,需要有一个定时脉冲序列,让收端可以识别到。在本次设计中将 “11100111”这个序列作为这个定时脉冲序列,在位同步识别到这个序列时,就会开始接收传输过来的码元。

......

研究内容

所研究的时分多路复用系统中的时分复用是成立在抽样定理基础上的,它可以对任一特定的通话进行呼叫,为其配置一个固定速度的资源信道,且保证之后的整个通话区间内信道是专用的。时分复用把若干个不相同通道的数字信号,根据其固定位置来分得时隙,聚合在有一定速度的传输信路上,这个信路称为一个基群[3]。在本次论文中主要论述了是同此次设计相关的一些基本原理的介绍,例如:位同步原理,帧同步原理等。并且在第三章中记录了所构建的时分多路复用系统的基本框图以及时分多路复用系统设计过程。第四章记录了在设计过程和验真过程中遇到的一些问题。而第五章则是展示设计成果。

本次设计利用了FPGA的仿真技术来实现多路信号的时分复用。成功地将三路数字信号合为一路的数据流进行传输,并最后成功恢复成三路信号。通过本次系统的设计和实现,通过查阅资料,重拾VHDL语言,使用软件仿真等方式方法,使得自己对FPGA更熟悉,以及对FPGA的QuartusII9.1软件的设计平台的操作又更加的熟练。这其中遇到过许多设计上的问题,比如位同步识别不到帧头或者延时太久等问题,最后都一一破解。几个月的时间里,从毕业设计的选题到研究,从一筹莫展到一步一步做出自己想要的成果,收获颇丰。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc1003,word全文:27页,合计:8800字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于FPGA的时分多路复用设计实现(论文)!

当前位置:

当前位置: