基于VHDL FPGA的异步串口通信控制器设计

[关键词:VHDL,FPGA,串口通信,控制器] [热度 ]| 提示:此毕业设计论文完整版包含【论文,源程序】 作品编号:txgc0423,word全文:24页,合计:11000字 |

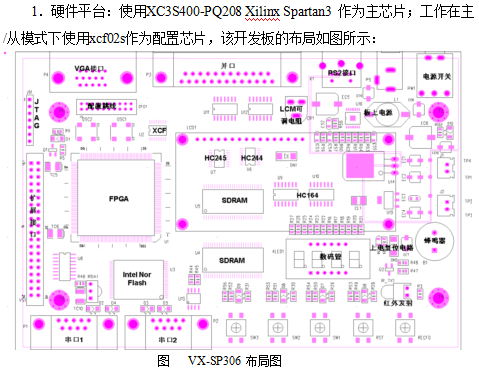

本课题采用Top-down设计方法学,通过对系统功能划分模块来进行设计。首先对各功能模块进行设计、模拟、验证,再对整个系统组合起来进行模拟、验证,最后利用利用FPGA进行硬件验证。结果表明设计正确,功能良好。

全文共分六章,其中,第三、四、五章是本文的重点章节。主要阐述了课题研究的方法、内容和结果。

第一章,论文通过分析目前国内外集成电路的发展现状及IP核的重要性,论证了设计一个UART IP软核的意义,并介绍了相关主要技术。

第二章,详细介绍了UART工作原理。

第三章,按照设计思想,阐明具体设计该系统。首先阐述了设计的UART主要功能,接着介绍了各模块的功能。

第四章,给出各功能模块的时序仿真图,证明设计的正确性。

第五章,详细介绍基于FPGA硬件验证的设计和验证方法。

第六章,总结了课题所做的工作和取得的成果,也对在课题进行中一些心得进行了总结,最后进行了课题展望。

论文通过设计异步通用收发器UART这个SOC系统中常用的IP软核,对可重用设计方法学进行了积极的研究和有意义的探索,一方面为IP核的设计提供了实践经验,另一方面也丰富了我国的IP软核库。本文的工作和已取得的成果对于国内系统集成芯片领域的IP核设计和重用技术具有一定的研究参考价值。

本文是关于IP软核的设计。IP软核是用VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。软IP通常是以硬件描述语言HDL源文件的形势出现,应用开发过程与普通的HDL设计也十分相似,只是所需的开发硬软件环境比较昂贵。软IP的设计周期短,设计投入少。由于不涉及物理实现,为后续设计留有很大的发挥空间,增大了IP的灵活性和适应性。其主要缺点是在一定程度上使后续工序无法适应整体设计,从而需要一定程度的软IP修正,在性能上也不可能获得全面的优化。

课题主要工作:

1.研究可重用设计方法学,明确设计规范和设计流程。

2.熟悉和分析UART串口的输入输出系统,明确论文的设计目标,确定各种具体的指标和参数。

3.使用硬件描述语言VHDL实现UART功能,在模块级别进行全面的功能验证后,使用EDA平台完成逻辑综合,静态时序分析。

4.在系统级别对UART进行功能仿真验证,使用FPGA开发平台,对UART串行接口和计算机标准串行接口的兼容性进行验证。

5.论文所实现的UART接口具有良好的可配置性,可作为独立的IP模块嵌入到其他SOC系统中。

| 提示:此毕业设计论文完整版包含【论文,源程序】 作品编号:txgc0423,word全文:24页,合计:11000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于VHDL FPGA的异步串口通信控制器设计(论文,源程序)!

当前位置:

当前位置: