基于VHDL的数字时钟设计和时序仿真

[关键词:VHDL,数字时钟,时序仿真] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0247,word全文:45页,合计:10000字 |

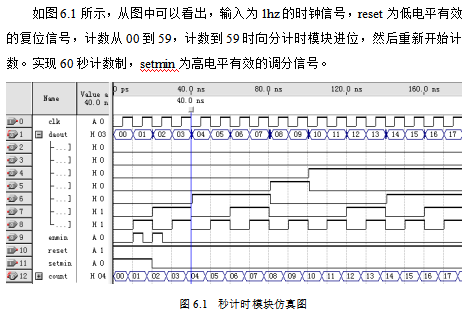

本课题需要使用VHDL语言,在Quartus II软件环境下,设计一个多功能的数字时钟,其中:

设计要求:

1) 在Quartus II开发环境中,结合FPGA开发板编译和仿真数字时钟;

2) 能显示时间:时、分、秒、月、年;

3)能进行时间设置。

指标要求:

a) 功能模块包括:时、分、秒等计数模块,报警模块,时间数据动态扫描模块和显示模块;

b) 对所有显示内容能进行调节设定。

本设计所研究数字时钟采用的方法是用VHDL语言输入,在Quartus II软件环境下编译程序,并且结合FPGA开发板进行时序仿真直至整体实现。由于使用了分模块化的设计思想,可以将整个设计分为多个底层模块,分别进行编译和仿真,然后根据原理图输入的方式生成顶层文件,进行整体设计的编译和仿真。由于采用了具有多层次描述系统硬件功能的“自顶向下”(Top -Down)的全新设计方法,极大地提高了电路设计的效率和可操作性。在信息化社会飞速发展的今天,EDA技术正是我们需要掌握的核心技术。

本设计对EDA技术进行了简明的阐述,叙述了VHDL语言的设计特点,主要论述了怎样在Quartus II 软件平台的基础上,设计一个以VHDL语言为输入的数字时钟系统。该系统可以在数码管上显示小时、分钟和秒,可以使用复位开关使系统时间清零;并可以在认为时间不准确的时候调节时间。不足之处是,由于时间、设备以及其他方面的因素,没能够把数字时钟的扩展功能:年、月、日显示出来,本设计已经可以满足对电子时钟的日常需求。本设计采取的是分模块化的设计过程,其中底层模块全部采用VHDL语言输入,而顶层实体模块采用了原理图输入的方式进行,根据由VHDL生成的各模块加上必要的器件,最后进行连线组成系统原理图。另外,顶层模块也可用VHDL语言来描述,采用这种方法进行设计需要的源代码将在附录里做详细说明。通过本次毕业设计,体会到EDA技术的先进性,用VHDL语言进行设计的优点,和Quartus II软件的强大功能。掌握了数字时钟设计的开发原理和基本思想,由此进一步扩展了我的思维,加深了对电子设计自动化的认识。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0247,word全文:45页,合计:10000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于VHDL的数字时钟设计和时序仿真(开题报告,任务书,论文)!

当前位置:

当前位置: