基于FPGA的数字扫描变换器的设计

[关键词:FPGA,数字扫描,变换器] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0321,word全文:50页,合计:24000字 |

本课题研究内容和本论文主要工作

本着立足自身、立足现实,努力提高自身技术,向国际先进技术进发的原则,本课题准备针对现在国内数字化B超诊断仪由于自身平台、超声数据处理和超声成像实现技术的限制,在处理速度、机器性能、稳定性、成像质量和功能扩展方面都有很多不足这些缺点,着力进行数字扫描变换器的开发,希望能得到一种新型的、操作方便的、技术含量高的扫描变换。它能与现有市场上的B型超声诊断仪兼容,但具有更好的数字图象处理能力,更方便的操作,能提高图象显示的速度和准确度,消除剧烈的闪烁,达到比较稳定的效果,为未来B超发展打下基础。

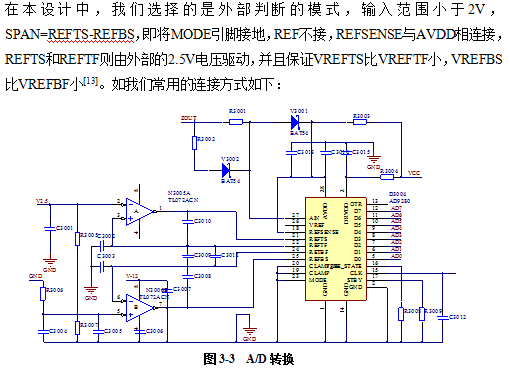

本文从B型超声诊断仪原理及全数字B型超声诊断仪设计入手,着重描述了数字扫描变换器的原理,结构,使用意义,并深入介绍了各种B型超声诊断仪的数字扫描变换器的硬件结构,并结合FPGA开发平台,得出了一种基于FPGA的数字扫描变换器的设计方法,通过各种参数选择,确立具体芯片完成各个结构功能,在Protel平台上绘制原理图,并导入,制成PCB板。由于FPGA在这个设计中作用很重要,主要完成对各个芯片的控制,所以我们又编制了控制程序,主要有对A/D逻辑控制,A/D逻辑控制,在图象存储方面,我们主要涉及乒乓操作对图象信息的存取控制,完成图象数据的存储和读取。最后根据程序得出仿真图,验证设计结果。

本设计中使用的D/A转换芯片及其特性

在本次设计中,我们使用了MAX5100芯片作为D/A转换器,它的性能如下:电压范围是+2.7V至+5.5V、低功耗、四路、并行8位DAC,满摆幅电压输出转换器封装在20引脚的DIP和SSOP中。MAX5100提供双缓冲逻辑输入。主要引脚如下:

OUTA、OUTB、OUTC、OUTD:DAC的A、B、C、D四个电压输出端;

A0、A1:DAC的地址选择端;

REF:标准电压输入;

SHDN:停止,将SHDN连接到GND是正常工作状态;

WR:写输入,低电平有效,数据输入的门闩由A0、A1选择;

D0-D7:数据输入端口。D0为数据最低位,D7为最高位;

LDAC:DAC的输入,低电平有效。

......

从图中,我们可以看出,与向SRAM写数据一样,我们从SRAM中读数据也可以用状态机和计数器,在控制信号和时钟源作用下完成。其主要流程也是如写数据一样。当RESET信号进入后,系统复位,进入状态1,并设定计数器的初值COUNT=0;复位后开始进入下一个状态,开启SRAM1的片选和输出使能CE1、OE1,从SRAM1中读出数据,并启动计数器COUNT;当计数器到达规定值时,从SRAM1读数据这个状态结束,转向IDLE状态,并关闭SRAM1的输出使能和片选OE1、CE1;接着转向下一个状态,从SRAM2读数据,开启SRAM2的输出使能和片选OE2、CE2,同时计数器计数,直到写满,计数器停止;此时到IDLE状态,等待下一操作,并关闭SRAM2的输出使能和片选OE2、CE2;然后又转向SRAM1读数据,周而复始。

......

在本论文中介绍了DSC的基本原理、体系结构以及在超声诊断仪中的应用,尤其是详细介绍了一种简单的基于FPGA的数字扫描变换器的设计,讲述了设计所使用的芯片,FPGA芯片的内部逻辑框图以及FPGA功能的VHDL实现等。研究的目的是为了解决B型超声扫查中,由于扫描速度等问题引起的图象闪烁等问题,提高B超的图象质量,使它有更广泛的应用。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0321,word全文:50页,合计:24000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于FPGA的数字扫描变换器的设计(论文)!

当前位置:

当前位置: