基于FPGA的等精度频率与相位计设计

[关键词:FPGA,等精度,相位计] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0317,word全文:40页,合计:20000字 |

本设计的具体工作包括:

(1)深入了解M/T法测量频率的技术,包括:信号预处理、在一定时间对信号计数、计数器数据的存储和处理以及控制信号的设置。

(2)研究对两个信号求相位差的方法,以及通过频率和时间差求相位差的算法。

(3)用VHDL和QuartusII中集成的宏模块配合完成设计,VHDL主要是完成信号预处理和信号周期计数以及译码显示,而计算主要是利用宏模块完成。

(4)在硬件实现中,功能选择等控制模块所需信号是通过一系列开关实现的,而数据的显示是通过8段led数码管实现的,系统的时钟(标准)信号又实验箱上的晶振通过FPGA的J3脚引入。

在后续章节中,第二章将简要介绍频率相位测量计的基本原理方法以及各项参数的计算方法等;第三章将介绍等精度频率与相位计的结构划分;第四章将讨论频率相位测量计的软件实现和系统仿真;第五章将对系统功能调试、测试方法及结果做详细阐述,指出存在的问题及可能的解决方法/思路。

在第三章中,会详细介绍设计的硬件结构图,使读者对设计有一个具体了解,在第一节中,先对所选用的FPGA器件及其开发环境进行介绍,让读者对FPGA和设计所用的实验箱的资源有具体了解;在此基础上,在第二节中,具体介绍了系统的各个模块的结构和信号流程,使读者能够深入了解课题的硬件设计思想。

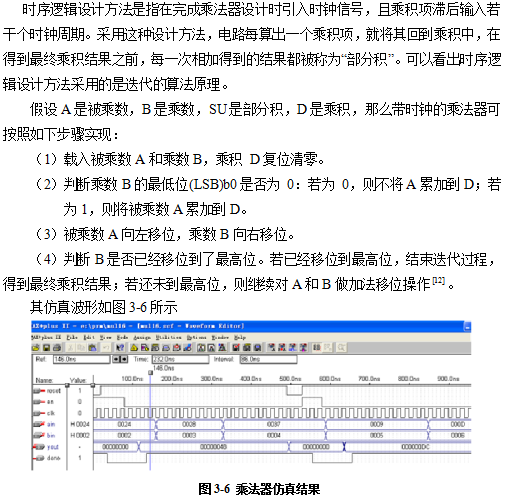

在设计中,共调用了三个模块,分别是乘法器、除法器和RAM。在测量占空比时,需要两个数据做除法,而这两个数据不是同时采集到的,是通过控制信号分两次采集,然后进行出发,这就需要把第一次采集的数据存储起来,以便在全部数据采集完后仪器进行处理,所以需要两块RAM用于存储。计算模块的硬件结构如图3-7所示。

本文结合工程需要从信号频率和相位检测的原理出发,通过查阅大量国内外文献,给出了等精度测量频率、脉宽和相位的算法。而后在分析算法结构和其中相关计算数据流动特点的基础上,对基于FPGA的实现方案进行大量和深入的研究。针对算法硬件实现的结构特征,笔者结合FPGA芯片的特点提出了设计的实现方法,并把方法通过模块划分,功能模块的设计过程中,本文采用了VHDL语言和LPM宏功能相结合的方式,既提高了系统性能,又使系统得以更有效率的实现。最后,在Altera的Quartus II软件平台上,对整个系统进行了全面的仿真,结果表明对频率和相位的测量从速度和精度上都满足了要求,而且间接显示了FPGA芯片处理高频率信号的优势,使本次设计的目标得以很好的实现。

本文通过将FPGA芯片与先进的相位检测算法结合起来,完成等精度频率数字相位计的设计。实验结果表明,这种相位计在精度和速度上均具有一定的优势。经过这次的设计工作,笔者也看到了一些不足,明确了下一步工作的重点:

在相位测量时,更为精确的算法是基于FFT的算法,而不是本设计所采用的先求出相位差,在通过正脉冲测量电路求得相位差脉冲,从而求得相位差。为此笔者构思了一个DSP+FPGA的处理系统。DSP作为主控制芯片,控制整个系统的处理流程,FPGA作为相位检测模块,完成相位检测算法的实现。整个系统在DSP的控制下采样原始采样数据,并启动FPGA的运算模块,当检测到FPGA运算结束信号,读回FPGA运算后的数据,进行数据测试分析。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0317,word全文:40页,合计:20000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于FPGA的等精度频率与相位计设计(论文)!

当前位置:

当前位置: