π4-DQPSK信号的FPGA实现

[关键词:π4-DQPSK,信号,FPGA] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0114,word全文:55页,合计:25000字 |

本人所做的工作及文章内容安排

本论文完成的是 π/4-DQPSK 调制解调研究和 FPGA 实现的工作。从大量文献资料来看,目前 π/4-DQPSK 调制解调器大部分都是采用专用芯片或者 DSP 硬件平台来实现的[2][6][20][23][24],也有采用 FPGA 来实现 π/4-DQPSK基带部分处理[21],全数字式调制解调仍在进一步发展中[22]。本人的工作主要包括:π/4-DQPSK 调制解调算法的 Matlab 设计仿真。在 Xilinx ISE5.2 开发环境下编写 VHDL 程序实现调制解调中的各个模块,通过了功能及时序仿真,从而保证程序正确性。分析了具体实现过程中采用的 1bit 差分检测误码率,推导误码率表达式,静态高斯噪声下,信噪比为 16dB 时误码率可达 10-8。在 Protel 99SE 环境下完成 PCB 板设计,程序下载进 FPGA 芯片以及电路调试,验证程序的正确。

本文的内容安排如下:

第一章:绪论。主要概述了 π/4-DQPSK 调制解调技术的应用背景和FPGA 实现方案。

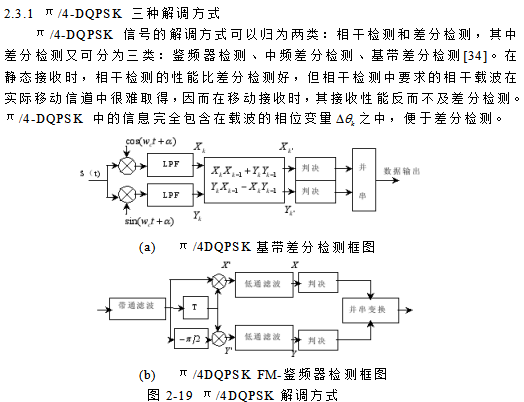

第二章:π/4-DQPSK 调制解调原理。主要介绍了调制解调的基本原理和其主要部分实现方案,如 NCO 数学模型、成形滤波器设计、中频差分解调优化算法、位同步实现。包括使用 Matlab进行滤波器设计、调制解调过程仿真。

第三章:π/4-DQPSK 的 VHDL 实现。介绍了 FPGA 设计流程、调制和解调模块中各个子模块的 VDHL 实现,在 ISE 环境下进行仿真。

第四章:硬件电路设计与调试。介绍了 FPGA 芯片和 PCB 板设计,VHDL 程序下载以及电路板调试。

第五章:误码率分析和全文总结。介绍了中频差分解调优化算法的误码率,并对本文进行全文总结和下一步工作建议。

本设计的仿真和硬件实现中,采用了一种更简单的新的 1bit 算法来实现 π/4-DQPSK 中频差分解调,该算法将接收的中频信号取其符号位,然后对中频信号的符号位序列进行差分解调,Matlab 仿真证明同样可以正确实现解调。该算法大大简化电路结构,大幅度的减少所占用的资源。图 2-21给出了该算法的实现框图。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0114,word全文:55页,合计:25000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——π4-DQPSK信号的FPGA实现(论文)!

当前位置:

当前位置: