QAM的FPGA实现研究

[关键词:QAM,FPGA] [热度 ]| 提示:此毕业设计论文完整版包含【论文,源程序】 作品编号:txgc0079,word全文:39页,合计:20000字 |

信号源模块

由上面的原理介绍,可以知道16QAM调制器的VHDL实现首先需要信号源,对于数字信号传输系统,传送的数字基带信号,由于载有的信息,在时间上往往是不平均的,对应的数字序列编码的特性不利于数字信号的传输;然后在接受端进行解扰操作,恢复到原来的信号。伪随机序列广泛应用于这类加扰,解扰操作中。下面是n=5的可以生成m序列的5级LFSR的特征多项式,即:,可以生成m=序列为周期的序列。当存储器内容为0时,对于m序列来说,起始序列为全0,那门输出也是全0,这不是我们想要的信号,因此我们的m序列发生器的模型

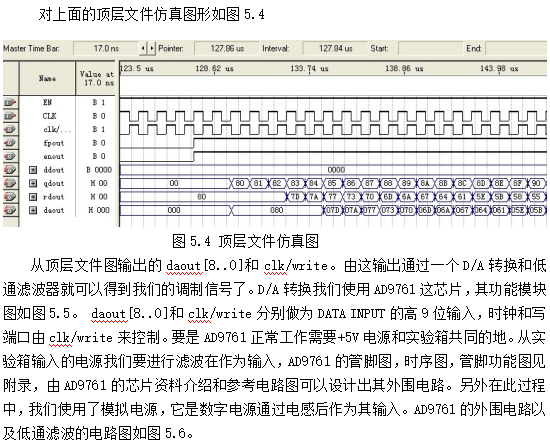

下面是顶层文件图,它是两个输入端口clk,en.时钟clk作为256分频模块,QAM相位调制模块,以及QAM幅度调制模块。En同时控制256分频模块,信号产生模块。QAM相位和幅度调制模块的使能端由专门的使能模块输出来控制,它是为了防止出现0.5个码元的延迟。在经过QAM相位调制后在DDS的ROM里进行寻址输出8位数据,然后进行QAM幅度调制,输出9位数据做为最后输出,也是我们调制的数字信号。另外一个输出clk/write是控制AD9761进行数据存储,D/A转换。

从顶层文件图输出的daout[8..0]和clk/write。由这输出通过一个D/A转换和低通滤波器就可以得到我们的调制信号了。D/A转换我们使用AD9761这芯片,其功能模块图如图5.5。 daout[8..0]和clk/write分别做为DATA INPUT的高9位输入,时钟和写端口由clk/write来控制。要是AD9761正常工作需要+5V电源和实验箱共同的地。从实验箱输入的电源我们要进行滤波在作为输入,AD9761的管脚图,时序图,管脚功能图见附录,由AD9761的芯片资料介绍和参考电路图可以设计出其外围电路。另外在此过程中,我们使用了模拟电源,它是数字电源通过电感后作为其输入。

| 提示:此毕业设计论文完整版包含【论文,源程序】 作品编号:txgc0079,word全文:39页,合计:20000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——QAM的FPGA实现研究(论文,源程序)!

当前位置:

当前位置: