FPGA上的FFT实现研究

[关键词:FPGA,FFT] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0035,word全文:53页,合计:16000字 |

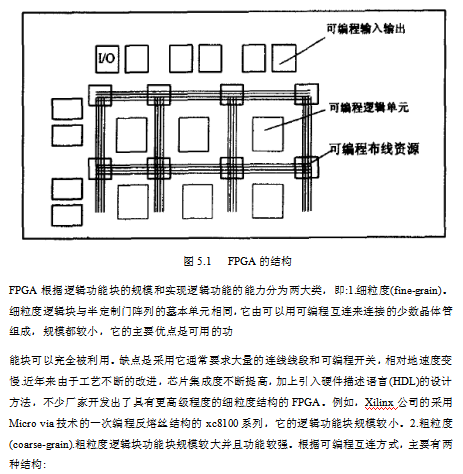

大规模可编程逻辑器件是近年来为适应专用集成电路设计需求而迅速发展起来的一类新型可编程ASIC器件。随着它的不断应用和发展,也使电子设计的规模和集成度不断提高。同时,带来了电子系统设计方法和设计思想的不断推陈出新。

本设计使用能够满足较高速度要求的FPGA(现场可编程门阵列)来实现一个在数字信号分析和处理领域重要的变换工具—FFT。FFT的算法是基2时域8点的FFT。通过C语言的的浮点以及定点的程序模拟,最终通过verilog HDL在Xilinx ISE 5.1i环境下进行编程和仿真。

本课题的目的和意义

数字信号处理是通信技术的重要组成部分,而在数字信号处理领域,离散傅立叶变换又是一个极其重要的变换工具,是对离散信号进行频域分析的基础。而对于大规模的频率变换而言,其计算量是庞大的,所以不满足实时高速处理的要求,所以衍生出FFT,就是使用快速算法来计算离散傅立叶变换。作为FFT算发的承载,器件必须适合FFT的要求,例如速度,FPGA以其多方面的指标是比较适合作为FFT算法载体的。这是本课题的物理基础。通过这个课题的设计,我们力求了解使用FPGA来处理通信范围的技术算法,通过这次课题设计掌握通过verilog这种硬件描述语言来进行具体数字应用开发的基础。通过这次课题设计去了解关于FFT的一些经典算法,例如基2时分。

本课题的设计步骤

在进行设计前,通过查阅各方面资料了解FFT的一些算法,了解其原理,决定选择一个算法,决定设计的点数。然后使用c语言进行算法浮点模拟,通过编译,得出结果,利用Matlab中所给的函数fft()对程序中输入的数据进行计算,用所得的结果和浮点C语言的结果进行比较,验证C语言fft源程序的正确性。一旦验证正确。然后再根据定点和浮点的关系,将该浮点C语言源程序改写成定点形式的,因为在FPGA涉及到的具体数据都是定点数,考虑到溢出和精度的问题所以使用这个中间步骤,这样用Verilog HDL实现时可以有个比较和验证,从而检查Verilog HDL的正确性。在证明浮点c程序的正确基础上,设置一些模拟的输入,得到正确的输出。而在编写c定点程序的时候可以以此组数据的定点结果作为检验标准,如果输出与标准数据相同就可以证明定点程序的正确性,一旦定点没问题,就可以按照定点C语言程序来写Verilog HDL程序。最后再利用软件如ModelSim和ISE等进行仿真和综合。

本毕业设计的重点是根据所选择的FFT算法分别写出浮点C语言源程序,定点C语言源程序和Verilog HDL源程序,并借助matlab,并一步步的验证。前步作为后一步的设计基础,直到正确的硬件输出结果。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0035,word全文:53页,合计:16000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——FPGA上的FFT实现研究(论文)!

当前位置:

当前位置: