数字频率计的设计和制作

[关键词:数字频率计] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0657,word全文:32页,合计:11000字 |

设计实现能对输入信号频率测量的频率计,并能在数码管上显示测量结果。设计要求:

1.调研频率计的功能和组成部分,并设计完成总体电路图。

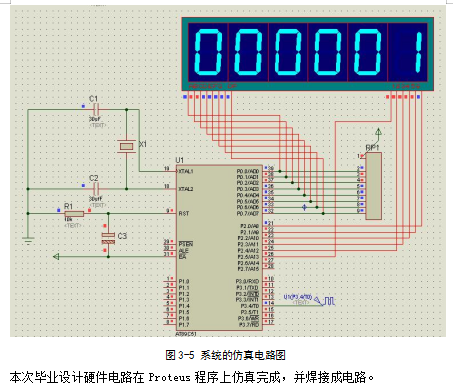

2.利用适当软件完成仿真设计与实验。

3.制作频率计实物,要求测量范围为2Hz-500KHz;测量相对误差±1%;能实现对正弦波、方波、三角波的测试。

系统计数过程

系统计数过程,是在标准间隔内,计数周期信号重复的次数,最后将结果显示出来。单片机AT89C51 内部具有2个16位定时/计数器,在定时器工作方式下,在被测时间间隔内,每来一个机器周期,计数器自动加1(使用12MHz时钟,每1μs加1),所以以机器周期为基准可用来测量时间间隔;同时可以由软件编程来实现定时。利用AT89C51单片机的T0、T1的定时计数器功能,来完成对输入的信号进行频率计数。

首先,被测信号在同步控制门的作用下, 产生一个与被测信号同步的闸门信号, 被测信号与标准信号(时基信号)在同步门控制信号的控制下。在计数器工作方式下,加至外部引脚的待测信号发生从1到0的跳变时计数器加1,这样在定时闸门信号的控制下可以用来测量待测信号的频率.其次,控制线路给出闸门开启信号,此时,计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器开始计数。然后,两组计数器分别对被测信号子和标准信号分别进行计数,要等到被测信号下降沿到来时才真正结束计数,完成一次测量过程。计数器的开闭与被测信号是完全同步的。在一秒钟的时间内, 对被测脉冲进行计数。当下一秒钟开始时,先将前一秒钟内所得到的计数值锁存并进行显示, 再将计数器清零后, 开始对下一秒钟的输入脉冲进行计数。外部输入在每个机器周期被采样一次,检测一次从1到0的跳变需要2个机器周期,所以最大计数频率为500kHz.定时计数没有溢出的最大计数值为65535.本频率计的设计以AT89C51 单片机为核心,利用它内部的定时/计数器,配合相应的前置信号处理电路、外围接口电路以及相应软硬件完成待测信号频率和周期的测量.

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0657,word全文:32页,合计:11000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——数字频率计的设计和制作(论文)!

当前位置:

当前位置: