基于CSD架构的FIR滤波器设计

[关键词:CSD架构,FIR,滤波器] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0748,word全文:52页,合计:16000字 |

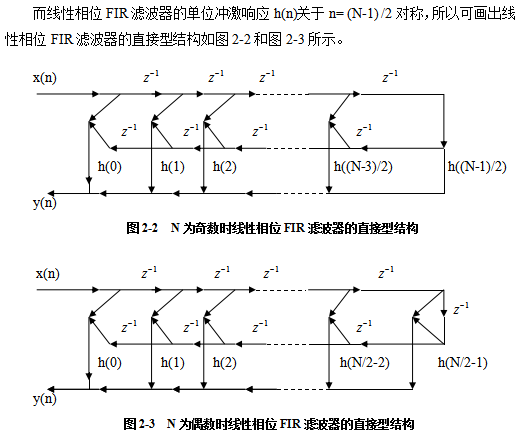

文中介绍了FIR数字滤波器的基本原理、应用领域及设计思想,比较了FIR滤波器各种实现结构的优缺点,并介绍了Matlab、ModelSim等软件实现低通FIR滤波器的方法及步骤,以此为指导,设计出了一种低通FIR滤波器。该滤波器采用了二的补码形式的CSD编码算法,能够将常系数编码中的非零位达到最少,从而简化乘法器的结构,提高滤波器的运算速度。滤波器电路采用Verilog HDL设计,最后设计出的基于CSD架构的半带FIR滤波器在ModelSim上通过了功能仿真,并在Matlab上进行频谱和时域分析。结果表明,此设计达到了预期效果,且采用这种方法设计的FIR滤波器其性能优于传统方法。

本课题所做的工作

1、要研究基于CSD架构实现的FIR数字滤波器,首先要了解CSD架构,然后才能进行下步的设计。

2、对FIR数字滤波器的结构和设计方法要有一定的了解,会使用MATLAB仿真软件设计各种FIR滤波器,以便对设计结果进行仿真和比较。

3、设计数字系统有多种方法,可以采用传统的数字系统设计方法,也可以采用使用硬件描述语言的数字系统设计方法。传统的设计方法不适合大规模系统的设计,所以就采用硬件描述语言的数字系统设计方法。这就要求学会自顶向下的系统设计方法、硬件描述语言Verilog HDL、综合工具、仿真工具ModelSim等。

4、采用CSD算法实现FIR数字滤波器,对CSD算法要有深刻的理解,并用Verilog HDL语言进行编程。最后用ModelSim对程序进行仿真分析。

本课题应解决的主要问题

本课题主要是用Verilog HDL硬件描述语言设计出一种基于CSD架构的低通FIR滤波器,在ModelSim上进行代码的编写与仿真,最后用MATLAB对所设计的滤波器进行时域和频谱分析,以使达到设计要求。

设计一个基于ASIC或FPGA的数字滤波器的过程包括图3-1所示的主要步骤。设计者可以用C语言编程来描述这种滤波器,而且必须能转化为可综合成能实现算法的硬件的Verilog RTL模型。但是此设计流程并不是很理想,因为必须要将用C写出的算法描述转换成Verilog格式,也就产生了出现错误的可能性。在C语言中,变量可表示为浮点数,但Verilog中的参数和其他数据值必须是定点、有限字长的形式。EDA提供商正在开发新的工具,以支持能够创建一个可执行并可直接综合的技术指标,同时可以省略翻译到HDL的中间过程的设计流。这些工具很有前景,但还未进入被广泛接受、应用的开发阶段[12]。

在本课题的设计与研究过程中,有所突破的地方如下:

1、使用硬件描述语言(HDL),可以用仿真方式完成以前必须设计和建造好样本才能进行的电子电路特性的说明和调试。可以使用仿真器测试所设计的电路功能是否正确,从而能够大大减少设计的成本和时间。

2、运用CSD编码来实现其架构且采用半带滤波器的方法来设计。由于CSD编码中非零比特数比二的补码的表示中要少33%,因此有效地减少了硬件实现所用面积和路径延时。在此基础上设计中还根据Horner法则来进一步提高系统的精度和面积,使设计的结果更准确。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0748,word全文:52页,合计:16000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于CSD架构的FIR滤波器设计(论文)!

当前位置:

当前位置: