一种Δ-∑模数转换器中梳状滤波器的设计

[关键词:模数转换器,滤波器] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0761,word全文:50页,合计:18000字 |

本设计的主要工作是完成Δ-∑ADC中数字抽取滤波器结构的第一级—梳状滤波器的设计,该梳状滤波器工作频率最高,所以功耗是最先要考虑到的。文中对级联顺序不同的几种梳状滤波器结构进行了功耗与面积的分析,力求达到最优化的面积、功耗。首先,在MATLAB环境中进行不同结构梳状滤波器的模块搭建,并搭建Δ-∑调制器模型以获取梳状滤波器的输入信号;然后,采用Verilog HDL设计滤波器,在ModeSim中进行调试与功能仿真,然后将仿真结果导入MATLAB进行频谱分析;最后将滤波器代码导入Synplify Pro 7.3中进行综合与优化。

......

由图2-4可以看出,调制器对输入信号有延迟作用,而且在输入端采用的是模拟正弦信号,所以在调制后得到的波形不是简单的均匀方波,而是以不同的占空比来体现正弦波特性,以达到将模拟信号准确的转换为数字信号。

为了方便以后用硬件描述语言Verilog HDL对梳状滤波器的设计,在此处,将调制器的输出信号以数据方式进行了提取,并保存在文档input_65536_6_20k.dat中

通过对Δ-∑调制器的分析,已经对噪声的形成有了初步的了解。将输入信号无损地传到输出端W(z)=1,量化噪声的传递函数,对应于频域的一阶高通滤波器(HP1),传输特性如图2-5中HP1线所示[3]。

......

本文主要完成了具有高精度的Δ-∑A/D转换器中梳状滤波器的设计,并进行前端综合与优化。论文的前半部分主要讨论过采样、噪声整形和数字抽取滤波的基本概念及梳状滤波器结构的选择;后半部分主要是完成对所选结构的设计、仿真、综合与优化。

整个系统设计都属于数字设计,其设计如下:

第一步,对Δ-∑调制器进行简要的分析,选择性能较好的3阶Δ-∑调制器在MATLAB环境中搭建出调制器模型,并输入频率为20kHz的正弦波信号,产生一串采样频率为10.24MHz的数字信号。

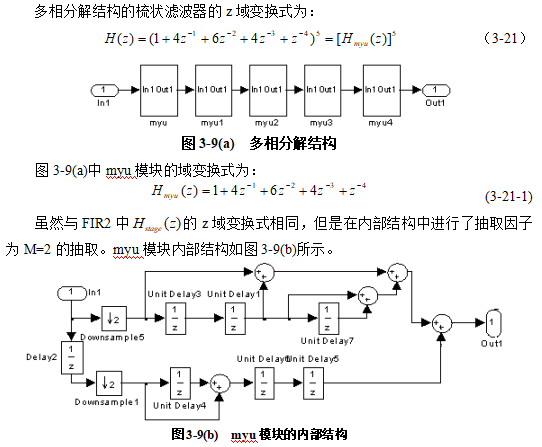

第二步,根据梳状滤波器传递函数的不同组合方式在MATLAB中搭建出直接级联型、IIR-FIR型、FIR2型和多相分解型结构的梳状滤波器模型,并将调制后所得的数字信号作为输入信号,进行仿真;对几种结构进行比较,选出相对最佳的多相分解结构采用Verilog HDL进行设计。

第三步,在多相分解结构中采用简单的移位加单元代替乘法器,大大降低了系统功耗和面积。将Verilog HDL设计出的多相分解结构梳状滤波器代码导入ModelSim中完成调试与仿真,得出通带衰减了0.2233dB,阻带衰减了119.3124dB。

第四步,将Verilog HDL代码导入综合工具Snyplify Pro7.3中进行前端综合,生成了综合网表文件cmb.vm,表明该滤波器系统可以综合。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0761,word全文:50页,合计:18000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——一种Δ-∑模数转换器中梳状滤波器的设计(论文)!

当前位置:

当前位置: