多路读写SDRAN控制器设计

[关键词:多路,SDRAN,控制器] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0181,word全文:50页,合计:22000字 |

本文选取了利用现场可编程门阵列(FPGA)实现同步动态随机存储器多路读写控制器的设计。并着重分析了设计中所用的SDRAM的性能、特点,给出了其初始化方式、相应的模式设置、读写时序状态转移图,提出FULL-PAGE模式下的SDRAM状态机设计方案。采用VHDL语言编程实现的控制状态机,可移植性强,易形成工程上可用的设计模块,在需要控制多路数据读写的应用中是较经济的。本设计在ISE开发环境中借助于ChipScope Pro 7.1、ModelSim SE 6.2b等工具软件进行仿真和综合,并在实际系统中通过测试验证了设计的实用性。

本设计的主要任务就是基于FPGA设计一个SDRAM控制器,让它可以工作在FULL-PAGE模式下,并形成工程可用的控制模块。

在上述应用背景下,本文主要做了以下几方面的工作:

1、了解常用内部存储器结构、工作原理和主流技术。

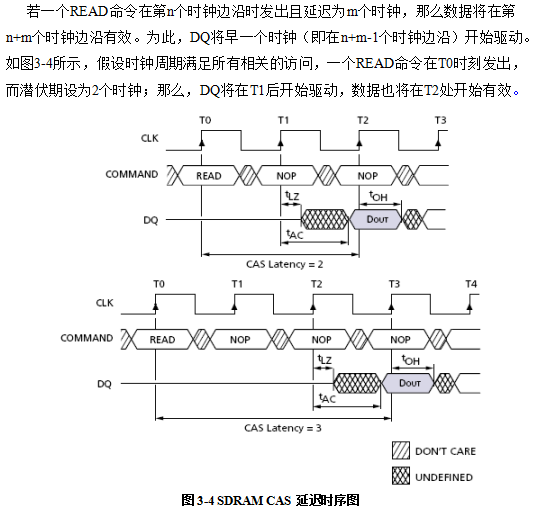

其中,简要介绍了内存存储技术的发展;联系本设计实际要求,着重介绍了SDRAM的主要信及命令、读写控制方式,分析了SDRAM在各种工作模式下的工作时序及其可行性等基础知识。

2、设计完成SDRAM读写控制器。

SDRAM是一种在外部同步时钟控制下完成数据读入和写出的DRAM。它像一般的DRAM一样需要周期性的刷新操作,访问前必须依序给出行地址和列地址。然而 SDRAM的输入信号都用系统时钟的上升沿锁存,使器件可以与系统时钟完全同步操作。它内嵌了一个同步控制逻辑电路以支持突发方式进行的连续读写,能够达到比传统异步DRAM快数倍的存取速度。而且只要给出首地址就可以对一个存储块进行访问,不需要系统产生和维持个别地址。另外,它具有的可编程工作模式和突发长度使其具体使用十分灵活。在本设计中,将基于FPGA、利用VHDL语言编程设计实现在FULL-PAGE模式下和突发模式下的SDRAM控制逻辑,设计实现多路读写控制器设计。

3、设计测试方案,在实际系统中测试通过。

在数据通信中,需要对上行或下行数据存储这些数据可能是突发的大量数据,也可能是固定的一定数据,因此要用到 SDRAM存储数据。因此设计需要一个SDRAM控制器,以便对 SDRAM进行控制。用 VHDL作为设计语言,具有简单、通用等优点。本设计通过对SDRAM的控制操作命令分析,设计控制逻辑完成SDRAM的读写操作,并通过并行状态机减小系统时延,提高吞吐率,形成工程上可用的设计模块。 依托科研项目所开发的实际硬件平台,在Xilinx公司的Spartan-3 FPGA中仿真、综合,并在实际系统中测试通过。

依据本课题的要求,本文的内容从以下几方面展开。首先对SDRAM进行简介,包括其存储原理、主要信号及命令等。接下来,着重介绍了SDRAM控制器的设计,包括SDRAM的读写时序、各种操作以及在Full-Page模式下控制器的工作流程等。最后是对SDRAM控制器功能的测试与分析,并对整个设计做出总结。

总结全文,主要完成了以下几方面的工作:

1.对常用内部存储器结构、工作原理和主流技术的发展等做了简要介绍;并着重介绍了SDRAM通用结构、规格参数、读写时序的分析等基础知识,这些都是更好地完成设计的重要基础知识。

2.并介绍了DRAM控制器的常用设计方法,并详细比较了它们的优缺点,选定本设计的设计方案是基于FPGA,利用状态机、VHDL语言实现对工作在FULL-PAGE模式下的SDRAM读写控制逻辑。

3.制定了测试方案,验证了设计的正确性和可行性,并分析了整个控制器的工作性能,完全达到了设计的要求。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0181,word全文:50页,合计:22000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——多路读写SDRAN控制器设计(论文)!

当前位置:

当前位置: