基于可编程逻辑器件的数据采集系统软件设计

[关键词:可编程逻辑器件,数据采集系统] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0482,word全文:62页,合计:20000字 |

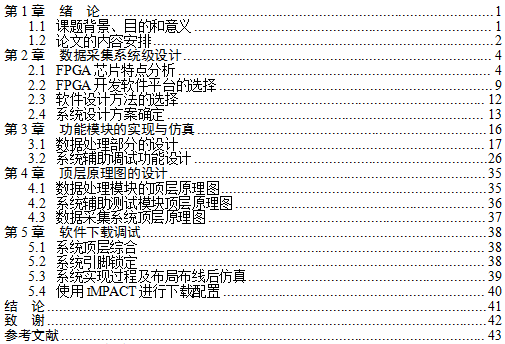

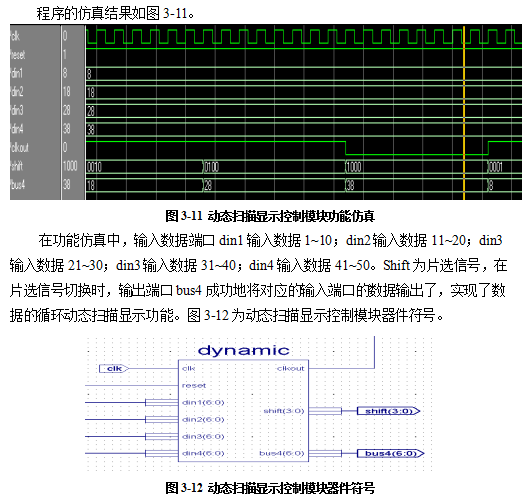

本论文介绍了基于可编程逻辑器件的数据采集系统的软件设计与仿真,使用VHDL语言在ISE 6.0的环境下设计,通过Modelsim软件对程序模块进行功能仿真。软件模块的设计用VHDL语言输入与原理图输入相结合的混合输入的方法实现,设计的显示部分包括七段数码管驱动模块和显示输出控制模块,显示输出用扫描显示输出方式设计,内部系统由多种功能模块组成并以原理图的方式设计实现,包括加法计数模块、扫描显示模块、信号发生模块、数据处理模块等。本论文对各模块进行具体分析并介绍了从设计仿真到最后生成顶层原理图,并用Modelsim完成最终的整体功能的验证,用ISE 6.0平台综合总程序然后下载的全过程。

通过本次设计,可以让我了解可编程逻辑器件FPGA的基本结构和用途,了解用FPGA芯片做系统设计的方法,也可以通过对VHDL语言的学习,熟悉软件与硬件结合设计的方法,通过VHDL语言对基于FPGA的硬件系统的控制,实现基本的数据采集的功能。通过设计过程,我将掌握现代数字系统的设计理念和方法步骤。

论文的内容安排

本文研究的主要内容如下:

(1)了解课题内容,查阅有关文献,了解FPGA结构、原理,熟悉FPGA技术,设计基本原则,学习VHDL语言及ISE 6.0开发软件的用法。

(2)了解数据采集系统的有关知识及项目要求,确定设计范围;整体上数据采集系统分两部分,即软件部分和硬件部分。硬件部分的设计应能保证系统的整体性能,采用资源丰富的FPGA来实现。硬件部分主要完成对FPGA芯片的接口电路的设计,以及必要的电源驱动电路和满足项目要求的其它电路部分的设计。本文主要完成软件部分的设计。

(3)本报告所涉及的设计内容,主要是对FPGA芯片的内部功能的控制和配置,以满足信号采集系统的基本功能为前提,用VHDL硬件配置语言来编程,实现采集信号的处理,显示等功能,同时还有内部自检信号的设计。

(4)论文其它部分还会对完成整个设计所需要的芯片做必要的功能介绍,因为软件设计要用到ISE 6.0开发软件,所以开始还会对ISE 6.0开发软件做简单的介绍。

(5)论文以软件设计为主要论述对象,按照整体设计思路,解释整个设计的实现方法和路径,最后具体说明软、硬件结合调试的过程以及最终设计成果的功能。

通过以上基本思路可以看出,整个设计将围绕几个模块来逐步实现,具体分为:

(1)数据处理模块;(2)显示模块;(3)信号产生模块;(4)A/D转换器控制模块。其中信号产生模块又分为:

(1)方波产生模块;(2)递增锯齿波产生模块;(3)递减锯齿波产生模块;(4)三角波产生模块;(5)阶梯波产生模块。

系统实现过程及布局布线后仿真

系统实现(Implement)就是将综合输出的逻辑网表翻译成所选器件的底层模块与硬件语言,将设计映射到器件结构上,进行布局布线,达到在选定器件上实现设计的目的。实现主要分为三个步骤:翻译(Translate)逻辑网表,映射(Map)到器件单元与布局布线(Place & Route)。右键点击Implement Design,选择Properties,可以对实现过程的三个步骤进行属性设置,本设计中默认软件的属性设置。双击Implement Design,实现过程的三个步骤依次进行实现,实现过程的一切信息都在信息显示窗口显示。

实现过程完成后,需要进行布局布线后仿真。将布局布线的时延信息反标到设计网表中,所进行的时序仿真就叫布局布线后仿真,简称布线后仿真。布线后仿真步骤必须进行,以确保设计功能与FPGA实际运行情况相一致。展开当前资源操作窗口的实现项目,双击布局布线项目下的Generate Post-Place & Route Simulation Model命令,产生布局布线后仿真模型。Xilinx 自动产生的仿真模型名为“top_timesim.vhd”。仿真延时信息文件名为“top_timesim.sdf”。后仿真模型文件自动调用SDF延时文件,将延时信息反标到仿真模型中。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0482,word全文:62页,合计:20000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于可编程逻辑器件的数据采集系统软件设计(论文)!

当前位置:

当前位置: