多次重触发存储测试系统设计

[关键词:重触发,存储测试系统] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文,源程序,答辩稿】 作品编号:ckjs0184,word全文:46页,合计:13000字 |

在本设计中,大体确定使用A/D转换器、存储芯片以及可编程逻辑器件作为核心部件,通过软件编程来实现CPLD对A/D及存储器的读写控制。其内容主要为:首先设计系统的硬件部分,用Protel99SE画出系统硬件连接图;用编写VHDL源程序;最后用ISE仿真工具进行仿真,得到系统的仿真时序。对应在论文中的章节安排如下:

第一章主要介绍本存储测试技术设计的研究背景、现状和意义,以及本设计所解决的问题和章节安排。

第二章介绍本次设计运用的CPLD 的概述 ,VHDL语言以及ISE的介绍。

第三章介绍系统硬件设计,包括硬件电路设计原理图和系统工作原理和系统框图,之后分别阐述了XCR3256对A/D7492的控制原理、对N08T1630的控制原理和A/D7492与N08T1630的配合工作原理。

第四章介绍系统控制设计,首先介绍CPLD对A/D7492采样的编程控制,其次介绍CPLD对N08T1630写操作编程控制最关键是推地址的控制每推64K等待下次触发信号来时才继续推地址,读操作编程控制最关键的是实现数据12并行串行输出到计算机。

第五章介绍系统仿真时序,对A/D采样控制的仿真时序、对存储器数据由并口转串口输出控制的仿真时序和和对地址控制的仿真时序。

第六章为结论。之后附有系统硬件设计原理图。

本论文采用存储测试理论设计了一个数据采集电路,完成多次重触发存储测试系统设计,本设计中选用A/D转换器AD7492、存储芯片N08T1630和CPLD芯片XCR3256设计了数据采集系统的硬件电路,用CPLD控制AD7492的采样和存储器的读写操作,关键程序是实现了每次触发存储64K的数据,存储存满满后发出满信号,计算机发出读信号进行存储器的读,在读过程中最主要的是实现数据的并串转换的输出,从而实现了多次重触发的存储测试。

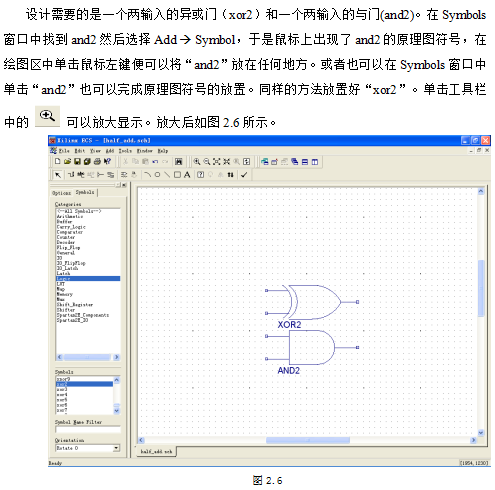

在系统设计时,首先设计了系统的硬件部分,用Protel99SE画出系统硬件连接图;其次用ISE的原理图输入设计了系统软件部分,并给出了硬件描述语言VHDL编写的源程序;最后用ISE的仿真工具进行了仿真,给出了系统的仿真时序。

综上所述,本论文设计完成了一个基于CPLD的多次重触发存储测试系统,符合设计所要求的多次重触发。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文,源程序,答辩稿】 作品编号:ckjs0184,word全文:46页,合计:13000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——多次重触发存储测试系统设计(开题报告,任务书,论文,源程序,答辩稿)!

当前位置:

当前位置: