基于C64xDSP的语音处理系统研究与设计

[关键词:C64xDSP,语音处理系统] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0285,word全文:48页,合计:21000字 |

本文各章内容安排如下:

第一章:首先是课题概述,提出课题的研究背景、主要研究内容、目的及意义,然后介绍了音频压缩技术的发展和现状,重点是语音压缩编码的三种分类,第三节阐述数字信号处理技术的发展。

第二章:首先大概介绍各个语音编解码标准,具体讲解它们的性能特征;第二小节主要内容是衡量语音编码性能的主要因素,主要是客观方法和主观方法,编码速率和编解码算法的复杂程度也是衡量其性能的重要因素。在本章的最后一节,重点阐述本课题用到的G.726的编解码算法的原理和特点。

第三章:这一章讲述DSP/BIOS的工作原理,DSP/BIOS实时内核能更快地开发和部署复杂的应用,并且用户不必开发和维护自定义的操作系统或控制环路,主要祥述了它的组成和工作过程。

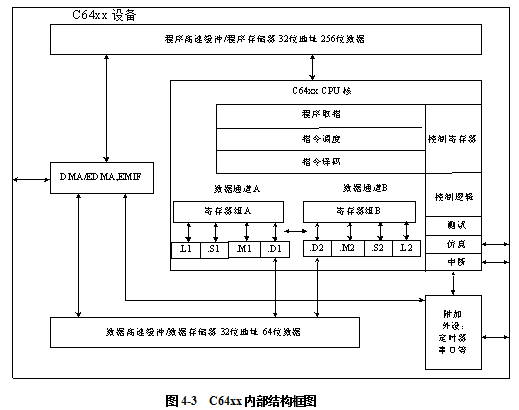

第四章:本章重点讲述G.726的算法实现,第一节描述系统的硬件结构并对重要的模块进行了介绍;第二节讲述初学者开发套件TMS320C6416 DSK硬件平台;第三节描述了集成开发环境CCS,最后两节讲述G.726的C语言实现和实时实现。

第五章:系统调试过程、指标和结果的描述,并对结果进行分析。

系统调试结论分析

在本课题搭建的系统中,语音编解码AIC23的采样率为48KHz,语音采样的速率快慢决定缓冲区数据填充的速度,数据缓冲的交替工作从我们DSK板上两个发光二极管就可以看得出来,如果采样率高的话,缓冲区很快就被填满,所以它们交替工作的速度也就要快一些。数据是等到缓冲区被填充满了以后才被传输的,语音编解码有延时,所以要协调好系统的时序才能使回放出来的语音效果达到最佳。

在上一小节中,我们发现了一个问题,那就是缓冲区的大小BUFFERSIZE太大,语音就根本回放不出来,下面就具体分析一下这个问题。

CCS上数据、代码和定义的缓冲区都是放在DSP6416的片上内存ISRAM上,查看DSP/BIOS的配置文件,发现ISRAM的长度设置为100000(十六进制),转换成十进制大约是1M个字节,如果我们将缓冲区的大小BUFFERSIZE设定为40K的话,又因为四个缓冲区的类型为INT16,即长度是2个字节,所以四个缓冲区所占的内存的大小为40K×4×2=320Kbyte,再算上代码占用的空间,这些所占用的总空间也不会超过ISRAM设置的长度。所以,排除了缓冲区定义过大导致语音不能回放的可能性。

系统数据的传输是靠EDMA进行的,而EDMA的传输一次最大的数据吞吐量是64Kbyte,如果我们将BUFFERSIZE的值定为40K的话,那么一个缓冲区所占的空间为80K,已经超过了EDMA的一次最大的数据吞吐量,数据就自然不能被传输,当然就听不到回放的语音了。既然EDMA传输一次数据的最大吞吐量是64Kbyte,那么,缓冲区的大小BUFFERSIZE的最大值就是32K,超过该值数据就不能被传输,也就听不到回放的语音了。

本课题在系统地研究G.726算法标准和TMS320C6416 DSP芯片特点的基础上,设计出一个基于TI公司的TMS320C6416 DSP芯片的G.726算法实时实现系统。经过几个月的努力,完成了在VC上G.726的编码标准的实现,并在硬件开发平台TMS320C6416 DSK仿真该系统,完成了语音的快速采集、编码和解码处理、回放,从仿真的结果来看,该系统的实时性好,基本达到了要求。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0285,word全文:48页,合计:21000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于C64xDSP的语音处理系统研究与设计(论文)!

-

没有关键字相关信息!

当前位置:

当前位置: