UART电路的VHDL设计及实现

[关键词:UART电路,VHDL] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,论文】 作品编号:txgc0095,word全文:46页,合计:17000字 |

本文介绍了用FPGA技术实现UART电路的一种方法,用VHDL进行编程,在Modelsim下进行编译及仿真等。

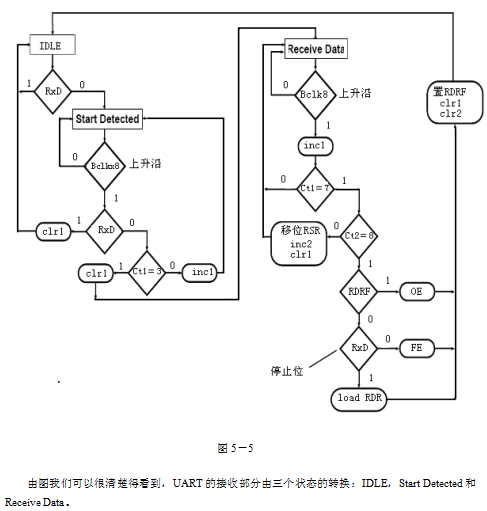

由图我们可以很清楚地看到:当RxD输入为1时,UART地状态为IDLE,接下来一位是0,状态便转为start_detective,也就是说明检测到了启动位,接下来就开始接收数据位recv_data,每8个时钟周期接收一位,当接收到8位之后,若下一位为1,则表示为停止位,RSR中的数据移入RDR中,这样便完成了一个字符的接收,图中显示接收到的数据为:10110010,与RxD端输入的完全一致。UART转入IDLE状态,准备接收下一个。

由图我们可以很清楚地看到发送状态地变化:由IDLE到SYNCH再到发送数据的TDATA。在发送数据时,bct在bclk的每个上升沿进行计数,将TSR中的数据一位一位地移出到TxD线上,并在移位后的寄存器前边的空位上填充‘1’,因此在TxD线上我们可以看到它的数据一次为01001101,与所要设计的要求很符合。

小结

本论文完成的预定的设计任务:

1.UART的接收功能,在输入端RxD端输入数据时,当遇到启动位‘0’时,UART

开始接收数据,同时计数器开始计数。接收器每8个时钟周期接收一位数据,若接收完8位数据后,接下来一位为停止位,则计数器清零,等待下一个启动位的到来。这样就完成了数据的串并转换。

2.UART的发送功能,计数器在每个时钟的上升沿开始计数,同时将TSR中的数据依次移到TxD端,完成数据的并串转换。

3.设计波特率发生器,使UART的接收和发送按照相同波特率进行收发。

4.设计总线接口及中断,使UART与总线之间能进行读写操作。

以上的VHDL设计程序均能在Modelsim下通过编译并进行仿真,其布线图和仿真图见上一章内容。

| 提示:此毕业设计论文完整版包含【开题报告,论文】 作品编号:txgc0095,word全文:46页,合计:17000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——UART电路的VHDL设计及实现(开题报告,论文)!

当前位置:

当前位置: