基于FLASH的高速存储测试系统设计

[关键词:FLASH,高速存储测试系统] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0517,word全文:39页,合计:14000字 |

本课题的研究任务与要求:

设计基于FLASH的高速存储测试系统,要求单通道采样率1M点/s,实现负延时,内触发与外触发功能,记录时间1s。本课题的主要目的就是,设计一个数据采集测试系统,对被测参数进行实时数据采集、存储。该系统主要完成对模拟信号的采集。

本课题在这种背景下,以FPGA为核心,加以高性能采集器件,设计实现了一个基于FLASH的高速存储测试系统。主要完成了以下工作:方案设计,讨论本课题所提出的应用背景与发展现状,确定了整体方案,给出了系统框图。然后讨论确定系统各个子模块的实现方法,并完成了所需芯片选型;完成硬件电路的设计,在下载查看了多款采集卡与FPGA开发板原理图之后,用Protel99SE设计了硬件电路图;对FPGA内部各子模块进行具体设计与仿真,利用VHDL编写分频程序产生系统所需的各种时钟;通过Quartus II设计了状态机来控制AD的数据转换,并对时序进行了仿真,最后利用FPGA内部IP核设计了数据缓存模块并进行仿真;系统硬件调试。程序进行了下载测试,确认了程序的正确性。

本设计具体要求及的论文内容安排

本次设计主要设计基于FLASH的高速存储测试系统,要求单通道采样率1M点/s,实现负延时,内触发与外触发功能,记录时间1s,结合理论分析的基础,设计出一个数据采集测试系统,同时利用该系统对被测参数进行实时数据的采集和存储。该该系统主要完成对4路模拟信号的采集。

本文具体内容安排如下:

第一章是绪论部分,介绍选择此课题的背景,并对本文主要准备工作和研究方法进行说明。

第二章主要是确定系统总体以及各个子模块的实现方案,并画出总体框图并分析描绘其工作流程。

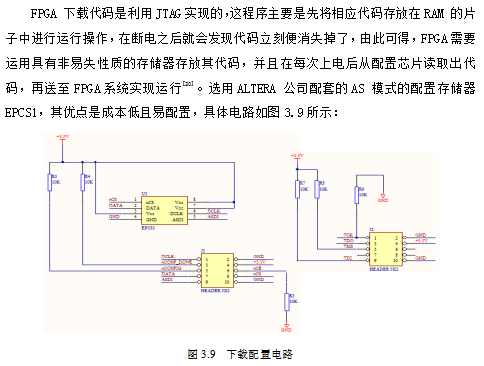

第三章主要介绍硬件电路设计。介绍了硬件电路的设计工具,对各具体模块中涉及的关键芯片进行选型分析,并给出硬件电路的详细设计。

第四章主要介绍了FPGA内部各模块设计。简单介绍系统的核心芯片后给出时钟管理模块的设计与仿真程序,然后详细讲述采集控制模块与缓冲模块的设计过程并给出了仿真波形。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0517,word全文:39页,合计:14000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于FLASH的高速存储测试系统设计(开题报告,任务书,论文)!

当前位置:

当前位置: