多通道FLASH数据存储系统设计

[关键词:多通道,FLASH,数据存储系统] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0213,word全文:45页,合计:15000字 |

课题要研究或解决的问题

容量小和断电丢失数据是本次课题要解决的问题,本设计采用CPLD 和单片机, 设计了一种基于Flash 闪存的大容量存储测试系统。单独采用单片机控制闪存时, 单片机的工作速度很难达到1Mbit/s 的采样速率, 如果靠外加扩展芯片来提高速率, 无形中又增加了测试系统硬件的复杂程度; 若单独采用CPLD 完成整个测试系统的控制功能, 则需选用较大容量, 且可用门数多的CPLD, 且内部控制时序相当复杂, 影响系统性能。故采用CPLD 与单片机相结合, CPLD 控制电路的时序状态, 而单片机负责闪存的读、写及擦除, 这样单片机和CPLD 的作用就能得到充分发挥, 不仅可以简化系统设计, 而且大大提高了整个测试系统的性能和稳定性。

课题拟采用的方法

本设计采用的Flash 闪存是K9F1G08U0A,AD 转换器采用的是AD7492, 最高采样频率可达1.5MHz,单片机是PIC18F8722。

本设计的内容以及待解决问题

本课题要求对基于FLASH存储的测试系统有较全面地了解,掌握国内外研究现状。掌握FLASH存储器的使用方法,给基于一种较大容量的FLASH 存储芯片,设计存储测试系统。主要解决当下存储器容量小,断电数据丢失的两大难题,根据本课题的实际情况,设计基于单片机的控制电路,完成简单的编程。

主要内容包括:

(1)根据所提出的功能要求,提出系统的总体设计方案;

(2)在总体设计方案的基础上,进行硬件电路的设计;

(3)CPLD内部时序控制模块的设计;

(4)单片机控制数据存储的程序设计。

本设计是基于单片机的大容量存储测试系统,本设计采用CPLD 和单片机, 设计了一种基于Flash 闪存的大容量存储测试系统。用CPLD 与单片机相结合, CPLD 控制电路的时序状态, 而单片机负责闪存的读、写及擦除, 这样单片机和CPLD 的作用就能得到充分发挥, 不仅可以简化系统设计, 而且大大提高了整个测试系统的性能和稳定性。

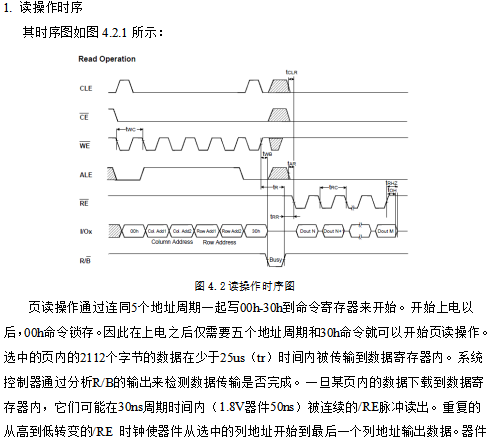

四路A/D转换器同步采集,同时将采集的数据实时的存入各自对应的静态存储器(SRAM)中。当系统触发以后,CPLD内部的负延时计数器开始计数,计数完毕以后,产生控制信号,将模拟电源,A/D转换器都关闭,此时,SRAM中存满了测试数据。单片机检测相关控制信号后,产生对FLASH写数的时钟控制信号,将四片SRAM中的数据依次写入FLASH中。之后,单片机产生控制信号,同时将模拟电源和A/D转换器都打开,等待下一次触发。每一次从SRAM中输出到FLASH的记录数据将按通道和记录次数存储。USB发出信号给单片机,单片机再控制Flash把数据读出来,通过USB传输给计算机显示出来。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:ckjs0213,word全文:45页,合计:15000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——多通道FLASH数据存储系统设计(开题报告,任务书,论文)!

当前位置:

当前位置: