循环码技术的研究设计

[关键词:循环码] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0739,word全文:46页,合计:21000字 |

本文的主要工作

本设计首先介绍了差错控制编码的基本理论,通过对线性分组码的研究,从而导出了循环码的基本原理,在此基础上进一步研究了汉明码的基本理论,最后推导出扩展汉民循环码的编译码方法。根据原理设计出一种(128,20)扩展汉民循环码的编、译码电路,并通过该设计的电路,在软硬件的基础上模拟实现了(128,20)扩展汉民循环码的编码与解码。循环码是线性码的重要的子类,而汉明码是典型的循环码,它们有严密的数学结构。结果表明(128,20)扩展汉民循环码(128,20)扩展汉民循环码的编、译码电路具有纠、检错能力,且编码、解码容易实现。在输入信息位,产生(128,20)扩展汉民循环码,通过调制,经过信道传输,然后解调再经过译码,传给受信者。

(128,120)扩展汉民循环码的译码电路

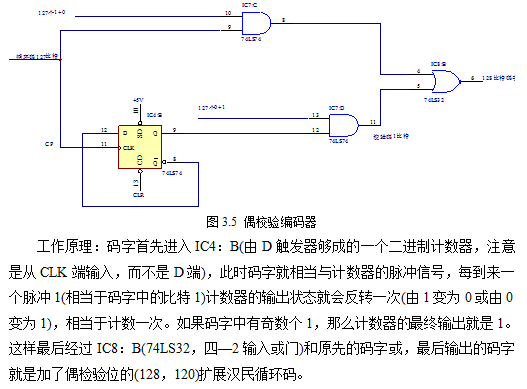

译码电路图如图3.6、3.7所示:

工作原理:被接收码字的前面127比特进入由IC1、IC2、IC3、IC4:A(74LS74,双D触发器)组成的除法器1,计算得到循环码的余式,如果它是0,则经过IC14、IC15:A、IC15:B(74LS32,四—2输入或门)后的输出A=0,否则A=1;码字的全部128比特全都要进入由IC8:A(由D触发器构成的一个二进制计数器具体电路如图3.5),如果码字有1位错,B=1,如果有2位错误,B=0;假设只有1位错误发生,在码字的第128比特,余式进入(并行输入)由IC5、IC6、IC7、IC4:B(74LS74,双D触发器)组成的除法器2,经过移位处理(串行输入,为解决并行输入和串行输入的问题,需在IC5、IC6、IC7和IC4:B的输入端加上IC9和IC10(74LS157, 同相输出四2选1数据选择器) 上面有个控制信号,高电平时为串行输入,低电平时为并行输入),在错码位置上经过IC13(74LS30,8输入与非门),再经过IC12:F(74LS04,六反相器)(其实两者合起来相当与一个8输入与门)后输出为1;在接收码字进入第一个除法器的同时,它也同时进入由IC18—IC33(74LS164,八位并行输出串行输入移位寄存器)组成的127bit移位寄存器,在8输入与门输出1的时刻,误码比特经过同样的移位也刚好到了127bit移位寄存器的最后1比特,此时两者经过IC11:D(74LS86,四—2输入异或门)异或后使误码取反,实现纠错。最后A和B进入逻辑判决电路(B要先进入IC17:A(74LS04,六反相器)取反后和A一起进入IC16:A(74LS08,四—2输入与门)进行逻辑判断)产生信号C,再根据C的值决定是否发出2位错误报警信号(具体的判决逻辑见3.2)。

本文主要介绍了扩展汉民循环码的原理和(128,120)扩展汉民循环码的软、硬件实现方法。硬件实现中主要完成了(128,120)扩展汉民循环码编、译码电路图的设计和绘制。软件实现中编解码方案的设计为了兼顾程序执行速度和减少存储器的占用量,设计数据表使用了功能强的高级编程语言Matlab语言,需要实时执行的编解码程序则是使用汇编语言来编写。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0739,word全文:46页,合计:21000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——循环码技术的研究设计(论文)!

-

没有关键字相关信息!

当前位置:

当前位置: