实验计算机的硬件设计

[关键词:实验计算机,硬件设计] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0610,word全文:35页,合计:14000字 |

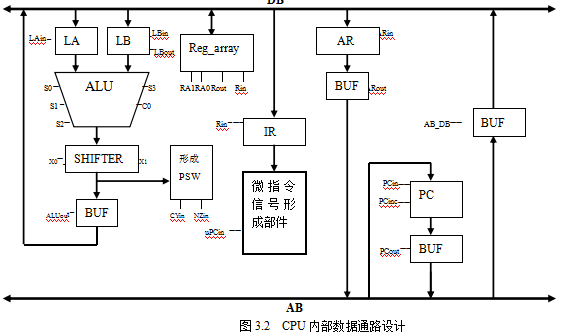

本文正是以此为背景介绍了可编程逻辑器件的设计方法和开发技术,并利用硬件描述语言 Verilog-HDL探索和设计了基于微程序控制的 8 位处理器。本设计采用了自顶向下的设计方法和模块化的设计思想,编写了处理器的代码,并具体阐述了寄存器,算术逻辑器件,指令译码模块,微指令形成模块的实现细节。通过对本设计的功能验证及仿真,表明该设计达到了预定的设计目标。在计算机组成原理教学中具有一定价值。

本文基于可编程器件设计实验计算机,不仅是想通过CPU的设计为教学改革做一点有益的探索,更重要的是借此来研究和探索基于FPGA的数字系统设计方法。当然,真正具有应用价值的CPU比本文所设计的要复杂的多。本文只是管中窥豹,从8位简单CPU设计出发,来初步探索CPU的设计方法。

本文的研究内容及设计目标

本文主要对8位CPU的硬件设计展开探索和研究,并对设计中采用的具体思想和出现的问题进行了阐述和分析。本设计要达到的目标是设计出能正确工作的CPU,在功能上予以仿真和验证,它能识别并执行三十多条指令,能寻址整个地址空间,支持多种寻址方式,达到实验教学的要求。

从图6.4可以看到,系统复位后,时序部件发出uIRclk为高的脉冲,系统进入取指令周期,在这个周期结束后,IR中锁存了第一条指令20(LD Ri,@addr)。接下来进入取操作数的周期,由于是间接寻址,我们可以看到AR先送入了0f,这是一个间接地址,在这个周期结束时,操作数14才送入了地址寄存器中。最后一个周期是执行指令周期,从波形图中能够看到,在这个周期结束时,寄存器组的R0单元确实写入了04。接下来的指令是源操作数为立即数的双字节双操作数的减指令。由于结果为负,在执行指令结束后我们可以看到PSW中C,N被置为1,同时触发执行JN 指令,PC不自增而是跳转到内存地址10。最后的4条指令是测试能否正确移位,同时置PSW。

通过仿真验证可知,结果与波形与设想一致,因此CPU的设计是符合要求的。

结束语

完成的工作及总结

本文利用硬件描述语言,采用了自顶向下及模块化的设计方法,完成了8位微程序控制CPU的设计。该设计层次清晰,基于状态机的时序控制使CPU工作节拍明确,寻址功能全面,指令丰富。仿真结果表明,该设计能够实现所要求的功能,从而达到了设计目标。作为实例,它可以应用到计算机组成原理的教学中。

该设计使我更加明晰了CPU的内部模块机构和各模块间的具体协作细节,特别是指令的执行控制过程有了较深入的认识。同时,学会了运用Verilog-HDL语言来具体实现设计思想。

改进与展望

当然,目前的这个CPU设计还很不完善,在功能上还很有限。为使其在功能上更加丰富,可以加入访问外设的部分,还可以加入堆栈,使CPU具有子程序调用和中断控制的功能。同时,可以增加寄存器组到8个。为提高CPU的寻址能力,总线可以提高至16位。为增强计算机组成原理教学的灵活性,还可以将CPU的数据总线参数化,可以选择8位也可以选择16位的CPU。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0610,word全文:35页,合计:14000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——实验计算机的硬件设计(论文)!

当前位置:

当前位置: