简易波形发生器的设计

[关键词:波形发生器] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0528,word全文:34页,合计:13000字 |

本设计实现一个基于SOPC 的任意波形发生器,不仅可以合成标准的方波、正弦波、三角波、锯齿波等常见波形,还可以通过PC 端软件合成用函数表达式描述的和手绘的任意波形。同时,波形的频率和幅度均可调节,输出频率范围为0.1Hz~1MHz,频率分辨率为0.1Hz, 输出电压范围为0~10V。

系统由三部分组成:SOPC 片上系统、D/A 转换与滤波电路和PC 端软件。

本设计中,相位累加器的位数N 为29 位,高12 位(即W)截断输出到片上RAM 的地址线进行寻址。因为系统时钟频率为50MHz ,则由式(2-4)得,频率分辨率为0.1Hz 。频率控制字FSW 的位数为24 位,最大频率控制字为101000111101011100001010 ,则由式

(2-2)得,最大输出频率为1MHz。DDS 模块的输入端为CLK 时钟和24 位FSW 频率控制字,输出端为12 位片上RAM 寻址线。其中,输入端FSW 频率控制字对系统的输出频率进行调制,输出端W 位地址线对存储于片上RAM 的波形数据进行输出。

首先模块由CLK 时钟输入触发而不断进行相位累加,相位累加器值为N,不断累加FSW 。24 位FSW 值由NIOSⅡ CPU 进行输入。当N 第29 位为1 时,相位累加器清零。然后将相位累加器高12 位,即第17 位到第28 位截断赋予W,最后输出。

波形仿真

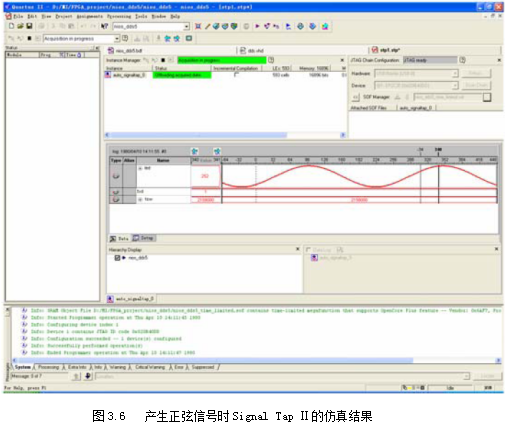

本系统采用QuartusⅡ开发环境中集成的Signal Tap Ⅱ嵌入式逻辑分析仪对信号进行仿真。利用Signal Tap Ⅱ可以在系统运行时捕获I/O 引脚和内部信号,将采样到的数据通过JTAG 接口上载到Quartus Ⅱ,显示为二进制、十进制和波形等各种形式。Signal Tap Ⅱ是高级的仿真工具,其必须连接硬件运行才能进行逻辑分析,所以不同于功能仿真,具有实时性和准确性,大大方便了系统的调试。在本系统中,产生的任意波形信号在尚未连接D/A 转换与滤波电路的情况下,可以通过Signal Tap Ⅱ观察生成的波形,而且逻辑分析结果随着信号变化而实时变化。系统产生的所有任意波形都可以通过Signal Tap Ⅱ仿真出来。图3.6 和图3.7 所示分别为产生正弦信号和方波信号时的仿真结果。

实验结果评估

本系统采用DDS 技术,通过基于NIOS Ⅱ的SOPC 系统实现了任意波形发生器。DDS技术在相对带宽、频率转换时间、相位连续性、正交输出、高分辨率及集成化等一系列性能指标方面远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能;而基于NIOS Ⅱ的SOPC 系统可以根据用户需要自由定制CPU 及其外设,其灵活性和通用性使其成为未来系统设计的一大趋势。

可以看到,本系统不仅可以产生方波、正弦波、三角波、锯齿波等常见波形,还可以实现真正意义上的任意波形。系统频率误差小于1%,且具有很高的频率调制精度,实验结果符合各项设计指标。

本设计完成了任意波形发生器的软硬件设计和调试,实验结果表明,该波形发生器基本达到了设计要求。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0528,word全文:34页,合计:13000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——简易波形发生器的设计(论文)!

当前位置:

当前位置: