基于SOPC的视频降噪系统的研究与硬件设计

[关键词:SOPC,视频降噪系统,硬件设计] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0392,word全文:46页,合计:22000字 |

全文的主要内容共分为六章,分别为:

第一章 绪论。综合介绍了图象处理的背景、应用展望,以及课题选择的目的和意义。

第二章 SOPC技术介绍。首先介绍了SOPC技术及实现的方式,然后介绍试验中所需要用到的软件QuartusⅡ的设计流程,最后介绍了硬件描述语言VHDL。

第三章 方案介绍、比较及选择。首先介绍几种典型的降噪方法,并比较它们的优缺点,然后按照其优缺点进行选择,从中选出自己的方案。

第四章 中值滤波的硬件实现。先介绍了中值滤波实现的总体框架,再具体介绍了框架中各个组件的功能及实现。

第五章 在SOPC中建立系统。先对组件进行选择并生成系统,然后再将生成的片上系统于硬件实现的滤波块进行连接,建立顶层文件。

第六章 功能模块与系统的仿真。先对各个模块进行仿真,然后再对系统进行仿真。

中值滤波模块的设计

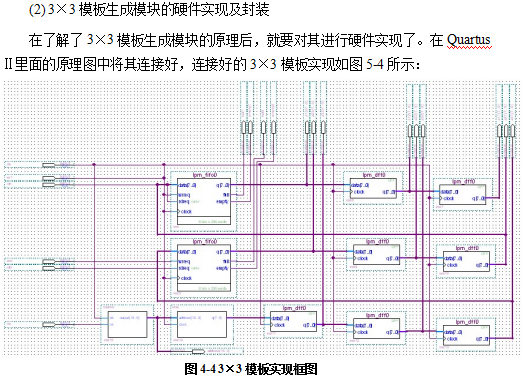

由于3×3窗口的中值滤波的效果最好,所以这里我们也选用3×3窗口。先是要设计一个3×3的模板生成块,其作用就是将数据按照需要的方式输出,就是将中心点和其周围的8个点的灰度值相对应的输出;然后输出的9个点的灰度值再经过中值滤波模块,这个模块的作用就是将9个数据进行比较后再排序,选出中间的数值即q5,再用q5的值代替中心的灰度值。

系统的调试及功能仿真

系统的实现是由硬件和软件联合实现的,软件部分主要是片上系统通过FIFO的满信号(full)来控制FIFO的读信号(rd),当满信号输出为1时,即FIFO里面存满了数据,则通过片上系统给FIFO的读信号置为1,让FIFO开始读出数据,因为只有当FIFO中存满了数据才能实现3×3模板生成模块的正确输出。在对系统进行仿真的时候,由于没有考虑到FIFO在写信号有效的时候,只要来个时钟周期就要存入一个数据,若没有数据输入则默认输入为0,所以在仿真的时候总是在输出的时候数据不对,因为我们是认为只有在有数据输入的时候才存入FIFO,而把0考虑掉了,所有得出的数据都不正确。通过多次得仿真和调试后,终于得到了比较满意的数据输出。而且通过数据能够看出系统确实是实现了对图像得中值滤波,这也说明了系统的正确性。

在此次设计中,我主要完成了以下工作:

(1)完成对片上系统的设置及系统的生成;

(2)完成了对深度为254位FIFO的设计及实现;

(3)通过硬件实现了3×3模板生成模块的正确输出,为中值滤波提供了实现的基础;

完成了中值选取模块的实现,并最终完成了整个中值滤波系统的功能仿真。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0392,word全文:46页,合计:22000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于SOPC的视频降噪系统的研究与硬件设计(论文)!

当前位置:

当前位置: