基于SOPC的视频图像压缩编码系统硬件设计

[关键词:SOPC,视频图像,压缩编码] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0381,word全文:70页,合计:33000字 |

本文主要研究了图像的5/3提升小波变换算法,设计了5/3提升小波变换算法的VLSI硬件结构。基于SOPC设计技术,完成了图像压缩编码系统的硬件设计。在EP2C70F672C6型号FPGA芯片上,采用QuartusⅡ软件对系统进行了综合、仿真,结果显示系统共占用1%的片上资源,耗时163.85us。论文给出了编码系统的总体设计硬件结构,并概叙了SPHIT压缩编码算法在NiosⅡ微处理器中的软件实现。设计的小波图像压缩编码系统实现了系统功能,并根据实际情况对系统进行了优化,减少了器件资源的耗用,提高了系统运行的速度。

本论文主要包含以下研究内容:

(1)详细阐述了小波图像压缩编码算法的理论知识。

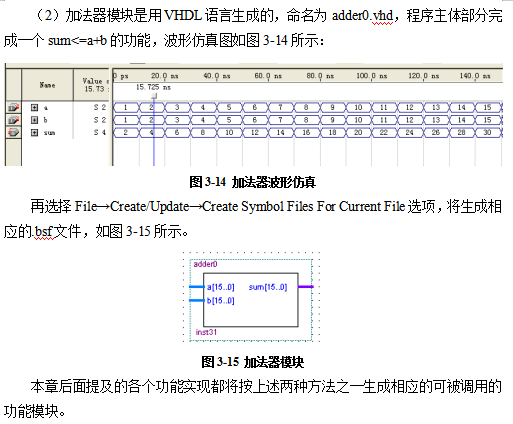

(2)深入研究了小波提升框架,实现了基于提升算法的图像二维离散小波变换,给出了二维图像5/3小波提升分解硬件结构设计方案,建立了VHDL硬件模型,并进行了仿真和逻辑综合。

(3)详细分析了SPHIT零树编码机理,对图像小波变换系数用C++语言进行了SPHIT编码算法实现。

(4)详细阐述了SOPC技术原理,深入研究了SOPC系统开发流程,采用Altera公司的SOPC解决方案构建了小波图像压缩编码系统。

通过对各个功能模块的仿真可以看出延时寄存器lpm_dff模块的输出有一个时钟周期的延迟,其结果导致图3-5中的奇序列端的输出信号H信号产生了一个时钟周期的延迟,偶序列端的输出信号L信号产生了两个时钟周期的延迟。这样,L信号比起H信号来说,产生了一个时钟周期的延迟,就达不到奇偶序列数据同时输入、同时处理、同时输出的要求。因此,为了满足后续的处理,需要在奇序列端的输出信号输出前加载一个延时寄存器。

各个模块都创建好以后,在工程中新建原理图文件,将前面生成的功能模块调出来按照图3-5的结构进行连线,并且在奇序列端的输出信号输出前加载一个延时寄存器,如图3-18所示。完成后,将此原理图文件命名为onewave.bdf,意思是一维小波变换。

系统总体设计方案

根据2.1.6节SOPC设计流程,SOPC系统是基于FPGA芯片,在其上嵌入了软核处理器、存储器、I/O口等相关模块的可编程系统,其设计具有软硬件协同工作的特点。因此根据实时性和重要性的需要,将整个系统的设计分为系统硬件实现和系统软件实现两部分。

如2.3节系统方案中提到的那样,硬件实现包括在FPGA逻辑单元上实现图像的提升小波变换,定制NiosⅡ处理器及相关组件和外设;软件实现包括用软件编程实现EZW的改进算法—SPHIT编码,以及编写NiosⅡ处理器的控制程序,从而软硬件协调工作,完成整个系统的构建。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0381,word全文:70页,合计:33000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于SOPC的视频图像压缩编码系统硬件设计(论文)!

当前位置:

当前位置: