一种高速采样的ADC控制电路设计

[关键词:高速采样,ADC,控制电路] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc1055,word全文:30页,合计:12000字 |

主要内容:

基于FPGA用VHDL语言设计一种高速采样的ADC控制电路,给出模数转换器ADC的基本原理和控制电路具体设计过程,利用开发工具QuareII对设计结果进行仿真验证。对此种设计方法是如何实现高速采样的进行简单分析说明。

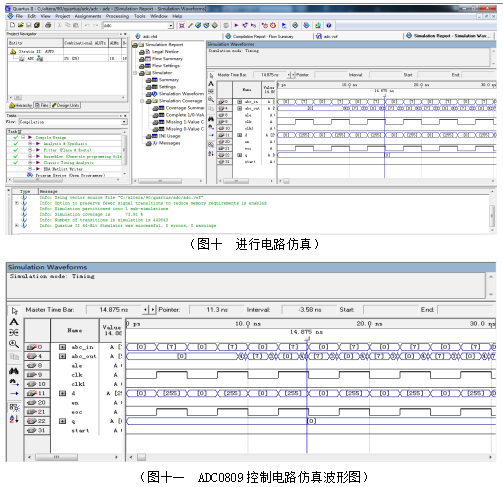

本论文给出了一种高速采样的ADC控制电路设计的方法。此控制电路是采用ADC0809芯片,利用FPGA器件高速高效的优点实现高速A/D转换。这种电路的特点是能与各种类型单片机系统友好连接,完成高速A/D采样和采样后的数据存储。本文具体介绍了完成高速采样ADC控制电路设计所需要了解的相关知识及包含FIFO存储器的采样控制电路的设计方法。最后给出了实现ADC采样控制电路所用的VHDL源程序和采样存储电路的设计方法,也给出了用Quartus II软件对所设计电路进行仿真测试得出仿真波形。

本文的章节安排和主要内容

第一章 主要介绍了本次设计的背景及其目的与意义。

第二章 主要介绍了模数转换器(ADC)的基本工作原理、ADC的主要分类及ADC的主要性能参数。

第三章 主要介绍了FPGA的工作原理、配置模式及特点,FIFO存储器、硬件描述语言VHDL及Quartus ii软件等的简单介绍。

第四章 主要介绍了ADC0809的主要特性、结构及工作时序分析,根据对工作时序分析进行控制电路设计,给出控制程序及电路仿真图。

第五章 主要介绍了采样存储电路的设计方法,给出了本次设计的ADC采样控制存储电路顶层电路图。

第六章 主要得出了本课题论述的结论及简单分析,对本次设计遇到的问题的解决方法简单说明,最后回顾大学四年及本次设计过程聊表谢意。

此次设计的高速采样存储电路采用lpm_FIFO参数化宏功能块,它的输入和输出共用一个端口,它的输入端口与ADC0809芯片的采样输出端相连,它的输出端与CPU的数据总线相连,当CPU读取数据时运用。AD_FIFO包括采样和数据读取两个工作阶段。在采样阶段,将WR_EN(输入控制信号)设置为高电平,CLK使能输入时钟脉冲信号,读请求rdreq被禁止,在某个采样周期中,当转换完成后,ADC0809转换得到的8位数据出现在数据总线D[ 7. . 0]上时,ADCINT发出的LOCK信号的上升沿就会把总线上的数据锁存进FIF02中;当结束一个或多个输入模拟电压信号的周期采样后就进入数据读取阶段,在数据读取阶段中,输入控制信号WR_EN被置为低电平,FIF02的读写时钟CLOCK通过MUX由RD_EN控制,在时钟信号的每个上升沿,FIFO2中的数据将逐一输出在端口Q[7..0] 上[12]。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc1055,word全文:30页,合计:12000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——一种高速采样的ADC控制电路设计(论文)!

当前位置:

当前位置: