简易逻辑分析仪研究

[关键词:逻辑分析仪] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc1050,word全文:24页,合计:10000字 |

基本要求:给出的这个设计题目没有很高的要求,主要以从实际教学实验为主,制作简单的逻辑分析仪,重点是要突出利用EDA技术,Verilog HDL语言来设计逻辑分析仪,并利用开发工具QuartusII的编译和仿真功能,实现逻辑分析仪结果的仿真验证。最后对设计出的逻辑分析仪的性能进行简单分析和优化。

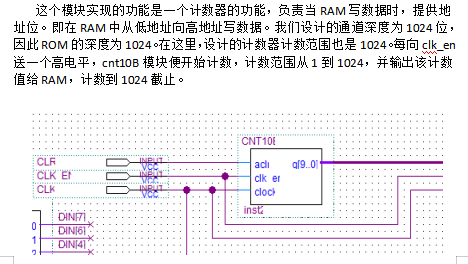

本课题是基于FPGA,设计简易逻辑分析仪。采用PC机和EDA技术,简单利用RAM进行数据存储以及一些辅助的器件,以Quartus II为软件设计平台,采用Verilog HDL硬件描述语言,设计完成一个8通道,深度为1024位的简易逻辑分析仪。在设计过程中,首先设计完成逻辑数据采样电路,进行仿真,确定电路能够成为一个8通道的数字信号采集系统。然后根据实验进行引脚锁定,完成编译和下载。被测的8路逻辑信号来自实验系统上的时钟信号源,利用Quartus II的SignalTapII测试采样的波形数据。对电路做一些改进,计入触发方式,将其设计成一个8通道,深度1024为的简易逻辑信号分析仪。

经过实际测试,满足设计要求,能够实现逻辑分析仪的基本功能。为教学和科研提供可用方便的波形分析工具。

课题研究的主要内容

本课题以研究逻辑分析仪为中心,进行设计和分析,只要设计完成一种在学习过程中,教学研究中可以方便使用的简易逻辑分析仪。

本设计是采用了八通道的设计方案。由于实验室条件限制,我们采用片内模拟逻辑分析仪的输入信号。我们在FPGA片内生成高频锁相环,用来生成几个不同频率的时钟,供逻辑分析电路采样分析。我们在设计内部加入74sl224锁存器,使用内部8个三态门来控制。

本系统的设计没有很高的要求,主要从学习实验出发,了解逻辑分析仪的基本原理,提高实践动手设计能力。对于学生设计而言,通过设计加深在数字电路,逻辑分析仪,微机原理,接口等技术的了解。

章节安排

第一章为引言,对设计背景、动态、内容、论文结构分布做了简明的介绍。读者可以对课题设计有相对整体的把握。

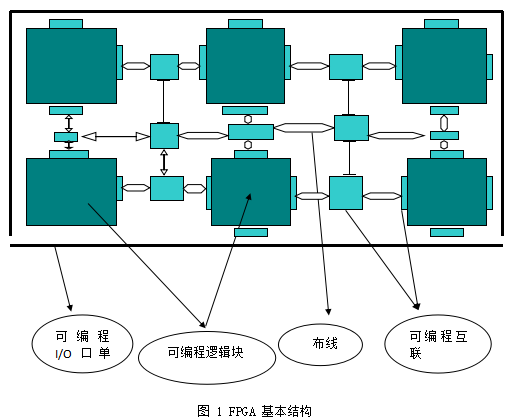

第二章FPGA技术相关概念,概念,设计流程,Quartus II软件平台介绍及。Verilog HDL硬件描述语言。

第三章为系统设计,先设计一个逻辑数据采样电路,再进行仿真,确定电路能够成为一个8通道的数字信号采集系统。

第四章完成逻辑分析仪的真题设计,包括加入锁相环。加入触发,完成一个8通道,深度为1024位的逻辑分析仪。

最后是对整篇文章工作的总结,简练的说明论文所做的工作,简要表达了设计成果和心得以及在此过程中的感悟。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc1050,word全文:24页,合计:10000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——简易逻辑分析仪研究(论文)!

-

没有关键字相关信息!

当前位置:

当前位置: