快速哈达玛变换设计与实现

[关键词:哈达玛变换,快速算法] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0756,word全文:40页,合计:15000字 |

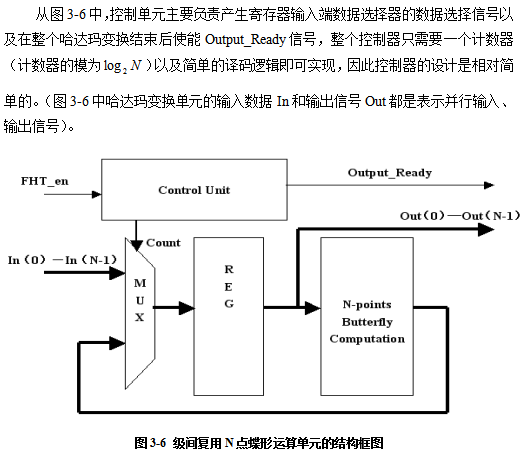

本文在研究哈达玛变换及其快速算法的基础上,分析了哈达玛变换的全并行结构,并根据其结构特性提出了哈达玛变换(FHT)的快速算法,快速算法的设计主要是从折叠结构出发,本文介绍了级间折叠和两点折叠这两种折叠结构,在FPGA中实现了16点快速哈达玛变换。结果表明在点数较多时用全并行结构实现哈达玛变换时的运算量很大,在用快速算法后运算量大大降低,在使用级间折叠时可节约资源数目,在使用两点折叠时可节约资源数目,从而达到大大节约资源的目的。

主要研究内容

首先,本文研究了快速哈达玛变换的基本原理,哈达玛变换的基本公式,以及它可以实现快速算法的原因;其次,快速哈达玛变换在FPGA中的实现也是该研究的一个重点。

论文的章节安排如下:

第二章介绍了快速哈达玛算法;

第三章介绍了VHDL软件的开发环境和具体的应用,主要是编程的应用;

第四章介绍了结合以上二者,用VHDL语言来进行快速哈达玛算法的设计及实现;

第五章介绍了实验调试的结果以及其分析;

本文介绍了级间折叠和两点折叠这两种折叠结构。对于16点的FHT在FPGA中的实现而言,级间折叠结构所消耗的资源近似为未折叠的一般结构的1/4,但级间与级内部折叠结构却并没有节省多少资源,这是由于复用引入了大量的数据选择器,而这些数据选择器的个数在FHT的输入点数比较少的情况下相对是比较多的,从而使得节约的资源并不明显,甚至在合并输入和结果寄存器后,资源消耗比一般的未折叠结构还要略多一些。

在图4-4中,有很明显的延时和毛刺现象,在QuartusⅡ中可以用时间线看出延时为:t=(51.809-50)ns=1.809 ns。但从总体来看,输出结果的时间还是在输入后的第4个时钟周期后输出的,只是有一定的延时,这在时序仿真里也是很正常的现象,另外,在图4-4中出现的毛刺现象也是这个原因,在前面的时序仿真概念里也有说明情况,为什么会有这些延时和毛刺的出现,他们都是在时序仿真是对器件的特性进行了考虑仿真,从而也就会出现这些情况了,这里也就不再对其进行更多的说明了。

这样,也就可以很容易的看出在图4-4中的输出结果跟图4-3中的输出结果是一样的,也就是可以说明在时序仿真中的结果是预期的正确结果,从而也就可以说明16点的快速哈达玛的原程序代码是正确的,进而在此基础上再往上加就可以得到64点及更多点数的快速哈达玛变换的程序代码了。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0756,word全文:40页,合计:15000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——快速哈达玛变换设计与实现(论文)!

-

没有关键字相关信息!

当前位置:

当前位置: