卫星信道模拟器误码插入的实现

[关键词:卫星信道,信道模拟器] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0746,word全文:42页,合计:17000字 |

课题设计的主要内容

误码插入是卫星信道模拟器性能测试以及故障诊断中必不可少的模块。传统的误码发生器基于CPLD和CPU协同工作,结构复杂,价格昂贵,而且不方便携带,随着现代EDA设计技术的进步,越来越多的功能将由硬件设计师集中在单芯片上实现。文章分析了误码发生器的需求,制定基于FPGA的误码发生器的设计方案,提出采用FPGA来完成误码仪的控制和测试模块一体化设计,提高了系统功能扩展性和系统的集成度,使得各个功能模块均可得到详细至逻辑门级的设计和改动。文章结构如下:

第一章对卫星信道及其特点,卫星信道的国内外现状,误码插入模块做了简单介绍。

第二章较为详细的介绍卫星信道的概念、总体设计方案,以及误码的概念。

第三章将介绍误码插入的总体方案、实现原理、电路组成。

第四章详细介绍了产生均匀分布的随机数的四种算法,通过分析比较选用线性反馈移位寄存法在硬件上实现均匀分布的误码插入。

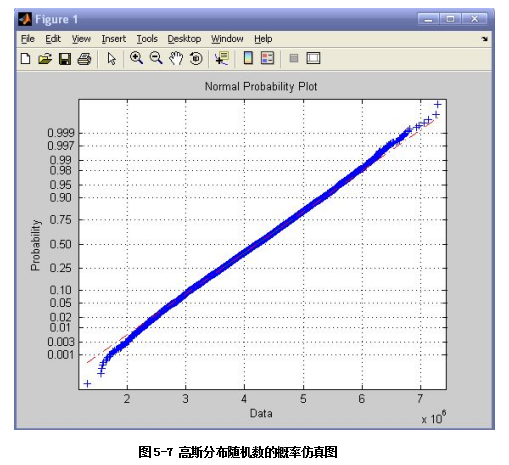

第五章详细介绍高斯分布实现两种算法,并对两种算法做分析和比较,选用用8个M序列叠加的方法在硬件上实现了高斯分布的随机数的产生,并且基于该随机数实现了高斯分布的误码插入。

第六章将简单介PC机和FPGA的接口设计,用VHDL语言实现串行异步通信。

根据设计要求本设计实现了以下功能:

1、能够对任意给定的误码率(101~106)产生均匀分布特性的误码图案,并根据此误码图案对任意给定的一组随机数实现均匀分布的误码插入。

2、产生高斯分布的误码图案,并对任意给定的一组随机数实现高斯分布的误码插入。

波特率发生器和采样时钟的设计

本设计采用的FPGA芯片的额定频率为50Mhz,串口助手工具采用的波特率为9600Baud/s,对应5208个全局时钟。当全局时钟为上升沿时,计数器开始计数,计到2605个全局时钟时,波特率时钟由之前的下降沿变为上升沿。并在5208个全局时钟中随意抽取3段时钟作为一个3倍频的采样时钟。

误码插入总体模块实现

在本论文的第三章已经讲述了均匀分布误码插入模块的设计方法,基于该方法的实现原理,论文实现了高斯分布误码插入模块的设计。

如图3-2所示,在PC机中用串口助手工具输入3个8bit的串行阈值TH,TH为通过PC机接口传给串口,串口在接收到数据后,进行串并转换,向比较器输入23bit的并行阈值TH。同时,随机数发生器产生一个高斯分布的23bit的并行随机数,范围在0- 223,并将随机数输入比较器。之后,与PC机输入的比较阀值TH在比较器中比较,当随机数小于TH时,输出“1”,否则输出“0”,即产生产生误码图案。从而完成高斯分布误码插入模块的设计。接着将生成的误码图案数据流与以E1接口输入的无误码数据流进行模2加后就生成了满足某一误码分布的数据流。再通过E1接口输出到误码仪中验证结果。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0746,word全文:42页,合计:17000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——卫星信道模拟器误码插入的实现(论文)!

当前位置:

当前位置: