微型计算机系统—存储器设计

[关键词:计算机系统,存储器] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:txgc0681,word全文:45页,合计:18000字 |

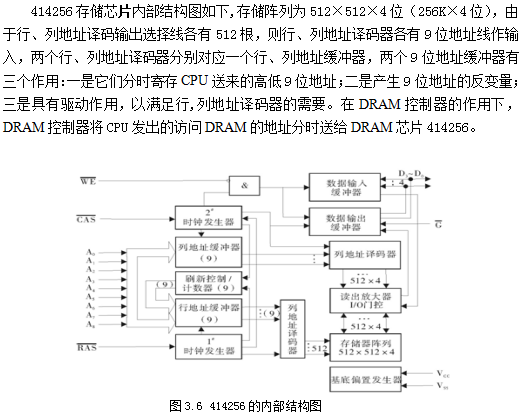

在深入研究和分析微机系统的存储结构和功能基础上,设计了一个较完整的存储系统,其中包括高速缓冲存储器,主存储器。主要完成了存储器和存储控制器的设计与仿真。存储器完成随机存储器,只读存储器和高速缓存的设计。随机存储器主要完成了动态随机存器芯片414256的设计,包括译码电路和存储体的设计。高速缓存完成了静态存储芯片M2114的设计和控制状态机的设计,存储控制器主要完成了DRAM存储控制器的设计,其中包括主要模块计数器,多路选择器和DRAM控制状态机的设计。

在设计中。采用数字电路设计方法利用硬件描述语言VHDL在MAXPLUS平台上进行的逻辑电路设计,程序设计以及仿真。大大简化了设计,从而提高了设计效率。

本课题的主要目标

本文是针对目前存储器的设计现状,通过VHDL语言来设计存储器,利用VHDL强大的硬件设计功能,来实现存储器的功能。

随着设计工艺的提高,存储器性能现在也有显著提高,但在进行实际的电路设计前,都需要利用像VHDL这种模拟软件进行逻辑设计,这样即能节省设计的时间,而且能够节省大量的设计成本,所以已经成为现在设计的主流。

利用硬件描述语言VHDL设计出一个较完整的存储系统,其中包括高速缓冲存储器,主存储器,主要完成存储器和DRAM存储控制器的设计和仿真,存储器完成随机存储器,只读存储器和高速缓存的设计。存储控制器主要完成译码器,计数器,多路选择器和cache和DRAM控制器状态机的设计。并对各个部分进行仿真。

在设计中。采用数字电路设计方法利用硬件描述语言VHDL在MAXPLUS平台上进行的逻辑电路设计,程序设计以及波形仿真。

随着存储器设计工艺的提高,存储器性能现在也有显著提高,但在存储器进行实际的电路设计前,都需要利用VHDL这种模拟软件进行逻辑设计,这样即能节省设计的时间,而且能够节省大量的设计成本,所以已经成为现在设计的主流。在这次的毕业设计中我也选择了VHDL作为开发工具,MAXPIUS为开发环境。

主存储器是存储系统中重要组成部分,计算机的运行速度和效率与主存储器有非常大的关系,,虽然现在的计算机的CPU速率和IO接口的速率有了极大的提高,但是速度的瓶颈现在已经是存储系统,而在存储系统中主存又是直接与CPU通信的,所以主存储器是计算机中极为重要的部分。所以主存储器也在不断的发展中,不但是存储的精度和广度要求越来越高,存储的速度同样也有越来越高的要求。这样可以把有限的资源用到更有用的部分。在设计该主存储器时,也考虑了这点因素,把存储器的实用放在了首位。而且该存储器能够达到精度和速度的要求。控制器是存储系统核心部分,一个存储器能否运行以及运行的效果如何都是由控制器决定的。在本次设计的控制器中,能够完成译码,编码和多路选择功能,这些功能是一个控制器的基本功能,虽然是独立的部分,但却是不可缺少的。以上的功能分别由译码器,计数器和多路选择器完成的。这些部件设计和运行已经达到了预定的水平。

主要内容:

(1)分析只读存储器、随机存储器(SRAM和DRAM)和高速缓冲存储器结构和原理。

(2)利用VHDL设计只读存储器、随机存储器(SRAM和DRAM)和高速缓冲存储器。

(3)使用Max+plusⅡ软件,仿真使用VHDL设计的只读存储器、随机存储器(SRAM和DRAM)和高速缓冲存储器。根据波形验证是否达到预期的设计目标。

拟达到的要求

(1)熟悉主存储器和高速缓冲存储器在微机系统中的作用,掌握微机系统中主存储器和高速缓冲存储器结构及工作原理;

(2)掌握使用VHDL语言进行硬件逻辑电路的设计方法及简单微机部件的硬件设计方法;

(3)掌握使用Max+plusⅡ软件编译VHDL源程序及功能仿真的方法,仿真波形的分析方法;

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文】 作品编号:txgc0681,word全文:45页,合计:18000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——微型计算机系统—存储器设计(开题报告,任务书,论文)!

当前位置:

当前位置: