基于异步SRAM的乒乓缓存控制器设计

[关键词:SRAM,乒乓缓存控制器] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0513,word全文:46页,合计:16000字 |

本文在研究FPGA的特点与VHDL语法结构及其优点的基础上,为解决大容量数据的缓存,针对FPGA中内部Block RAM有限的缺点,分析比较了FIFO、双口RAM、乒乓缓存结构几种电路的优缺点,提出了将FPGA与外部SRAM(IS61LV25616AL)相结合来改进设计的方法。讨论了乒乓缓存控制器的结构和原理以及实现, 而其核心的就是乒乓缓存控制器(包括读地址产生器,写地址产生器和数据切换电路,实现存储矩阵的行-列转置,读出数据的并-串转换)。还介绍了在QuartusⅡ6.0开发平台上,以FPGA开发板为基础进行了仿真和调试。通过调试证明该系统可以作为后续进一步开发扩展使用。

论文的主要结构

在阅读了大量资料明白本论文主要研究的是面对需要大容量的数据存储的情况,针对FPGA中内部RAM有限这个缺点,本文提出了将FPGA与外部静态存储器(SRAM)相结合的设计方法。本论文的结构安排如下:

第1章 主要介绍本课题的背景、目的及其意义。

第2章 主要介绍现场可编辑逻辑器件(其中比较了FPGA与CPLD)与VHDL语言的结构及其优点。

第3章 了解并介绍了SRAM的分类及其(IS61LV25616AL)的特点。

第4章 介绍了乒乓缓存控制器的设计思路及其实现。

第5章 程序的仿真及其调试,及在调试过程中遇到的问题及解决办法。

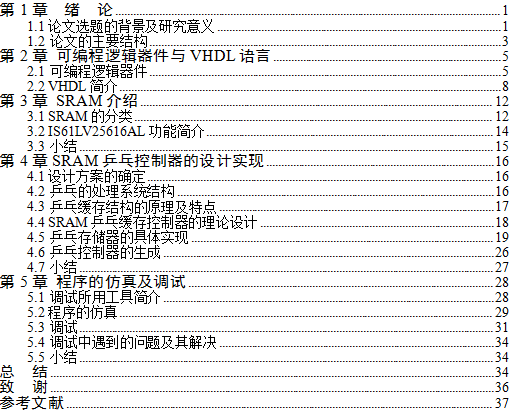

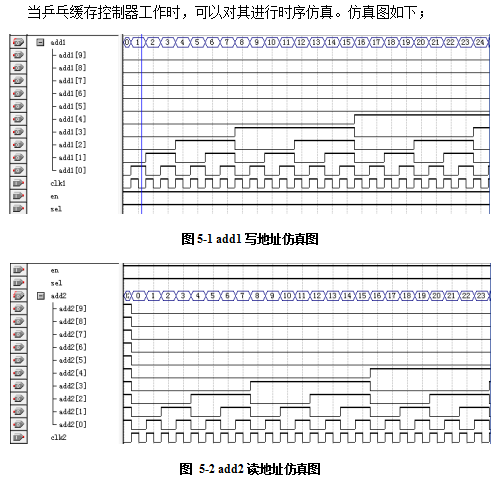

设计仿真

Quartus II软件允许设计者使用基于文本的向量文件(.vec)作为仿真器的激励,也可以在Quartus II软件的波形编辑器中产生向量波形文件(.vwf)作为仿真器的激励。波形编辑方式与MAX+PLUS II软件的操作相似。在Processing菜单下选择“Simulate Mode”选项进入仿真模式,选择“Simulator Settings…”对话框进行仿真设置。在这里可以选择激励文件、仿真模式(功能仿真或时序仿真)等,单击“Run Simulator”即开始仿真过程。

器件编程

设计者可以将配置数据通过MasterBlaster或ByteBlasterMV通信电缆下载到器件当中,通过被动串行配置模式或JTAG模式对器件进行配置编程,还可以在JTAG模式下给多个器件进行编程。利用Quartus II软件给器件编程或配置时,首先需要打开编程器(在New菜单选项中选择打开Chain Description File),在编程器中可以进行编程模式设置(Mode下拉框)、硬件配置(Programming Hardware对话框)及编程文件选择(Add File…按钮),将以上配置存盘产生.cdf文件,其中存储了器件的名称、器件的设计及硬件设置等编程信息。当以上过程正确无误后,单击Start按钮即可开始对器件进行编程配置。

本文针对FPGA中内部Block?RAM有限的缺点,提出了将FPGA与外部SRAM相结合的方法控制大容量数据的缓存。通过设计SRAM控制器,了解了FPGA技术应用在大规模集成电路设计中的方便和灵活性。知道了乒乓缓存控制器的结构和原理以及实现,并进行了大量的仿真和调试,通过LED屏进行验证。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0513,word全文:46页,合计:16000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于异步SRAM的乒乓缓存控制器设计(论文)!

-

没有关键字相关信息!

当前位置:

当前位置: