基于GW48系列实验平台的Nios2实验板设计制作

[关键词:GW48,Nios2,实验板] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0359,word全文:39页,合计:17000字 |

系统整体结构

由功能需求分析确定硬件结构原理图如图3-1所示:

系统模块基本组成:

(1)微处理器采用Altera公司生产的Cyclone系列的EP1C6Q240C8。

FLASH存储器:采用一片AMD29LV320D FLASH存储器,大小为4M字节,用于存放程序等。

(2)SDRAM存储器:用一片HY57V641620HG作为SDRAM存储器,大小为8M字节,可满足Rclinux操作系统及各种较复杂算法程序的运行要求。

(3)电源模块:采用AMS1117芯片对5V电源运算生成1.5V与3.3V电源。

CPU核心系统设计

本实验开发平台的系统核心是一块ALTERA公司的Cyclone系列的微处理器——EP1C6Q240C8为手持设备和一般应用提供了高性价比和高性能的微控制器解决方案。

JTAG电路

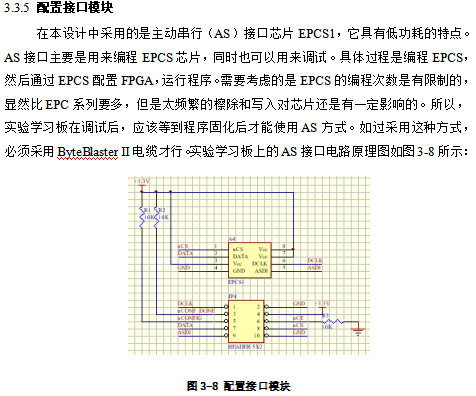

本设计中采用的JTAG接口电路源于已经十分常用的JTAG接口电路,参数主要来自于数据手册推荐匹配值。JTAG (Joint Test Action Group)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试。JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路,可以通过专用的JTAG测试软件对芯片内部节点进行测试。目前大多数比较复杂的器件都支持JTAG协议,如ARM、DSP 、FPGA器件等。JTAG接口常用于实现ISP ( In-SystemProgrammable,在系统编程)功能,如对FLASH器件进行编程等。通过JTAG接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁而高效的手段。

工作总结

本文对基于FPGA以及NIOS的嵌入式系统设计进行了深入的研究,并在此基础之上,设计完成了以Cyclone EP1C6Q240C8 为核心芯片的SOPC硬件实验平台。但是设计板未能与GW48实验平台很好的兼容,使得其在实用意义大为减弱,但增加了扩展I/O插槽,可以对设计版资源进行有效的补充。归纳起来主要做了以下工作:

(1)设计了具有自主版权的基于Nios II的SOPC系统平台。作为一块核心板,只保留了和嵌入式相关功能,包括处理器、ROM、RAM、总线接口、以及LCD接口等多种接口方便扩展,这样可以满足嵌入式系统体积和功耗大幅度减小的要求。

(2)板上设计了各种插件、JTAG、LCD接口、SDRM、按键显示等与用户交流的部件。

(3)归纳总结了基于NIOS II的系统硬件的设计方法和经验,完成了电路图的设计与制作。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0359,word全文:39页,合计:17000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——基于GW48系列实验平台的Nios2实验板设计制作(论文)!

当前位置:

当前位置: