白噪声发生器的设计

[关键词:白噪声,发生器] [热度 ]| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0117,word全文:34页,合计:11000字 |

研究内容

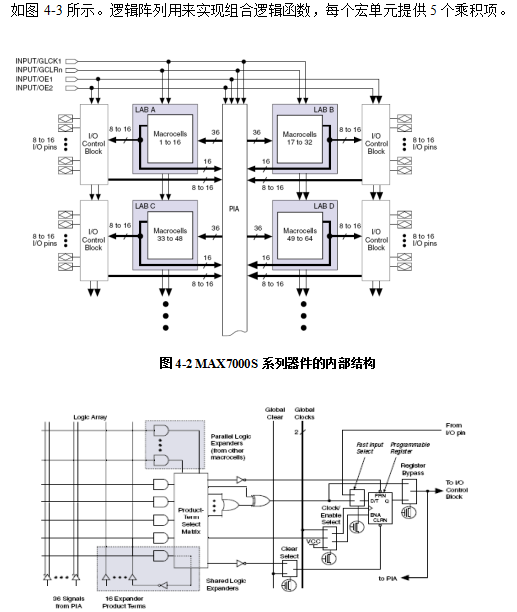

本设计是完成一个白噪声发生器的设计,在论文中主要介绍伪随机m序列产生的原理。并用MAX+plusⅡ软件进行仿真,然后设计电路图在面包板上焊接,将仿真通过的程序下载到CPLD的器件上,用示波器观察,最后再对仿真结果和调试结果进行分析和比较。经过比较和分析,白噪声发生器基本实现了功能,即利用CPLD产生一个16级的伪随机序列,该伪随机序列周期是65535,基本上是满足零均值的高斯分布。因实际使用只需白噪声的带宽远远大于基带信号带宽,所以伪随机序列通过一个1MHz的低通滤波器,输出的就是带限信号,将这个带限信号再通过运算放大器将噪声信号按需要放大相应的倍数,以获得不同的信噪比,通过加法电路实现有用信号和噪声信号的合路,实现实际通信中的现实情况。

我做的主要工作是:

(1)查阅各种芯片资料,选定合适的芯片。

(2)分析m序列产生的方法,选择合适的方法。

(3)用VHDL语言进行编写程序,使其实现伪随机序列的功能。

(4)在MAXPLUSⅡ完成电路的时序仿真。

(5)把程序下载到CPLD芯片中。

(6)焊接电路板。

(7)最后通过示波器观察分析验证结果。

通过了计算机的仿真,发现本设计的伪随机序列产生方法是可行的。通过了示波器的观察,在电路板上可以通过跳线的控制,使其产生八种不同的噪声放大幅度,放大后与原信号反相。放大后的噪声与调制信号的合路,即模拟了调制信号在信道中的实际过程。

综上所述,本设计基本上完成了预定的任务。

本设计应用CPLD芯片完成了白噪声产生器的设计。以MAX+plusⅡ为程序设计工具,利用VHDL语言编程产生伪随机m序列并烧录到EPM7064SLC44-7芯片上实现功能。在硬件设计方面,利用Protel99SE设计电路原理图在面包板上焊制。

用CPLD实现的系统,运行速度快,体积小,其外围电路以及一些扩展接口全部集成在芯片中,没有外部连线,易于管理和屏蔽。而且调试的工作很方便,电路调试出来的波形和理论上基本吻合。

| 提示:此毕业设计论文完整版包含【论文】 作品编号:txgc0117,word全文:34页,合计:11000字 |

本通信工程毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——白噪声发生器的设计(论文)!

-

没有关键字相关信息!

当前位置:

当前位置: