长线通信测试电路及软件设计

[关键词:长线通信,测试电路] [热度 ]| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文,答辩稿】 作品编号:ckjs0321,word全文:66页,合计:22000字 |

本课题要研究的问题

本课题是提供远距离数据通信测试功能。测试电路的主控制器在开关的控制下接收并行数据并存入FLASH,且可将数据存入电脑并显示。同时要熟悉FPGA和Flash的操作,熟悉高速PCB设计技术。控制芯片与LVDS转化器之间的并行数据传输速度为100 KBYTES/s~1 MBYTES/s;传输距离要大于10M;并行接口方式为光隔接口;此外还要将驱动器和中继子系统间的串行数据传输状态通过指示灯显示供观察,而且要求常规测试无误码。

本课题任务的实现途径

发送电路的主控制器在开关的控制下通过光耦合器接收8位并行数据,并存储与FPGA控制芯片中,再保存于FLAS存储芯片中,同时FPGA控制芯片中的信号传输于控制台并将信号存于计算机并显示。本子系统采用FPGA作为系统的控制芯片,实现对LVDS串化器的控制。LVDS串化器在FPGA的控制下接收通过光耦合器传送过来的信号,并将其存储于FLAS存储器中同时传于控制台并在计算机中显示。在信号接收端采用了光耦合器进行信号隔离,光耦合器在电气上是不连接的,因此可隔离输入、输出信号,起到电绝缘及抗干扰的作用。

论文内容和安排

这次的设计的主要内容是完成一种基于FPGA的长线通信测试电路及软件设计。主要进行一下几个方面的工作:

(1)研究掌握当前的FPGA、LVDS和FLASH存储技术的原理和优缺点;

(2)研究大量数据存储的FLASH实现方式,并作出电路图;

(3)研究FPGA控制下的LDVS接口,实际电路和版图;

(4)研究并串转换电路结构,设计电路和版图;

(5)研究数据缓冲电路以及辅助电路原理和结构,设计电路和版图;

(6)研究实时采集数据的PC显示,利用VB++或其他软件编写可视化的窗口显示数据;

论文的安排如下:

第一章讲述了本课题研究背景及FPGA、LVDS和FLASH基本介绍,并选定本次设计的主要芯片;

第二章详细介绍高速LVDS接口的原理、FPGA的原理以及大量数据的FLASH存储原理;

第三章主要介绍本设计中的所有硬件电路,包括FPGA、LVDS、FLASH存储、驱动器等配置电路,并作出详细的电路图;

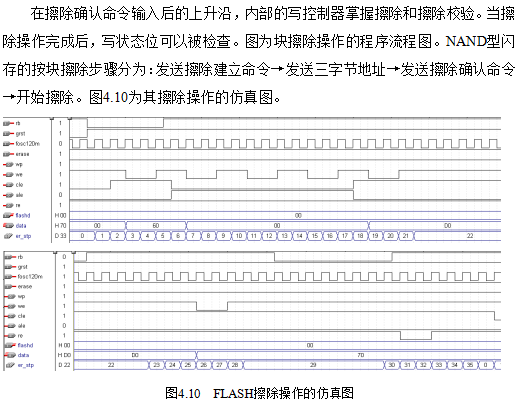

第四章详细介绍各种软件的流程,包括基于FPGA的数据采集程序流程、LVDS数据传输程序流程、FLASH数据存储程序流程以及PC机上数据的可视化程序设计,并进行部分仿真。

第五章总结整个设计,找出其中的不足之处。

论文完成了长线通信测试系统的硬件电路和软件程序的设计,基本上实现了以FPGA为中心控制器的数据采集、存储、传输和显示的功能。

主要对基于LVDS的高速串行链路进行了研究,论文主要从数据采集后处理的整个过程进行了分析,然后就FPGA设计中的各个逻辑功能模块进行了深入的分析并给出各个模块的实现方法,还对DS92LV1023专业并串转换芯片进行了介绍,同时还给出了针对每个模块以及总体传输性能的仿真图。在数据实时传输的同时,还实现了利用大容量FLASH存储器来储存采集到的大量的数据信息,保证了后期对数据的保存和处理。

文中所提出的LVDS数据传输设计方案,就是利用FPGA作为整个系统的核心来对系统时序和各逻辑模块进行控制。通过FPGA内部丰富的宏功能块资源来实现数据的缓存,并利用其内部精确的时钟系统为高速数据传输时的并串转换提供精准的时钟,同时还要控制FLASH芯片存储大量的数据。这样使系统能够顺利的工作在FPGA中控制下,实现高速数据传输。这种高速的LVDS数据传输方式在诸如高速数据采集系统、视频采集、多路数据采集等诸多领域得到广泛应用。

| 提示:此毕业设计论文完整版包含【开题报告,任务书,论文,答辩稿】 作品编号:ckjs0321,word全文:66页,合计:22000字 |

本测控技术与仪器毕业设计论文作品由 毕业论文设计参考 [http://www.qflunwen.com] 征集整理——长线通信测试电路及软件设计(开题报告,任务书,论文,答辩稿)!

当前位置:

当前位置: